국내 연구진이 엔비디아의 최첨단 칩인 A100 대비 소모전력은 625분의 1, 칩 면적은 41분의 1로 작은 인공지능(AI) 반도체 핵심기술을 세계 최초로 개발했다. 에너지 제약이 높은 환경에서도 정확하게 거대언어모델(LMM)을 구동할 수 있어 온디바이스AI 구현 등에 활용될 전망이다.

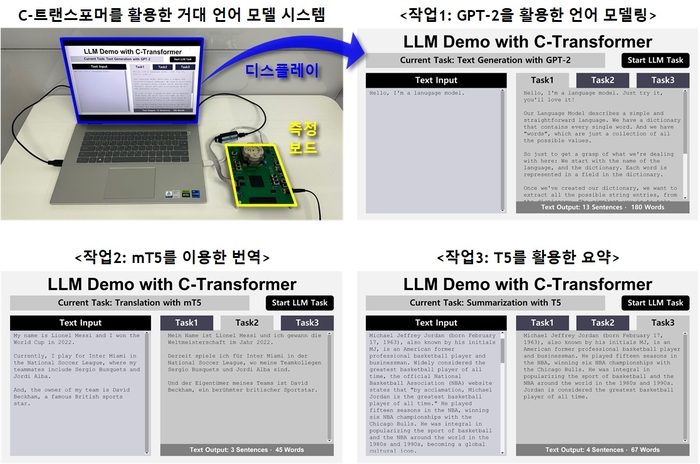

과학기술정보통신부는 한국과학기술원(KAIST) 프로세싱인메모리(PIM) 반도체 연구센터와 AI 반도체 대학원 유회준 교수 연구팀이 400㎽ 초저전력을 소모하면서 0.4초 초고속으로 거대언어모델(LLM)을 처리할 수 있는 AI 반도체 핵심기술인 '상보형-트랜스포머'를 개발했다고 6일 밝혔다.

인간 뇌의 동작을 모사하는 뉴로모픽 컴퓨팅 기술은 딥러닝 모델인 합성곱신경망(CNN)에 비해 부정확하며, 주로 간단한 이미지 분류 작업만 가능했다.

연구팀은 이번 연구에서 뉴로모픽 컴퓨팅 기술의 정확도를 CNN과 동일 수준으로 끌어올리고, 단순 이미지 분류를 넘어 다양한 응용 분야에 적용할 수 있는 상보형-심층신경망을 제안했다.

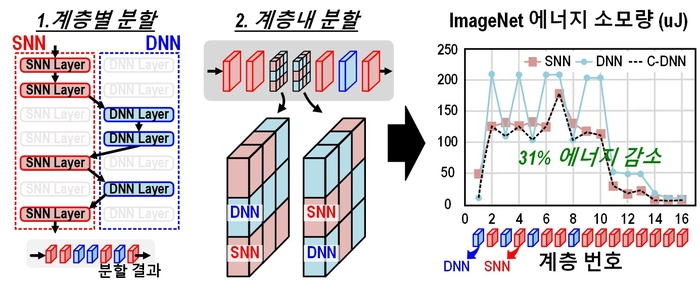

상보형-심층신경망은 복잡한 패턴을 인식하고 학습할 수 있는 AI 모델인 심층 인공 신경망(DNN)과 뉴로모픽 컴퓨팅의 한 형태인 스파이킹 뉴럴 네트워크(SNN)을 혼합해 입력 데이터들을 크기에 따라 서로 다른 신경망에 할당해 전력을 최소화할 수 있는 기술이다.

이번 연구는 상보형-심층신경망 기술을 거대 언어 모델에 적용함으로써 초저전력·고성능의 온디바이스 AI가 가능하다는 것을 실제로 입증한 것이다.

일반적으로 뉴로모픽 시스템은 에너지 효율이 높지만, 학습 알고리즘 한계로 복잡한 작업을 수행할 때 정확도가 떨어진다. 이는 거대 언어 모델과 같이 높은 정밀도와 성능이 요구되는 작업에서 큰 장애 요소로 작용한다.

연구팀은 이를 해결하기 위해 독창적인 등가변환기법을 개발해 적용했다. SNN의 에너지 효율성을 유지하면서도 DNN 수준의 정확도를 달성하는 방법이다.

이를 통해 개발된 AI 반도체용 하드웨어(HW) 유닛은 기존 거대 언어 모델 반도체 및 뉴로모픽 컴퓨팅 반도체와 비교해 네 가지의 특징을 갖는다.

DNN과 SNN을 상호 보완하는 방식으로 융합한 독특한 신경망 아키텍처를 사용함으로써 정확도를 유지하면서도 연산 에너지 소모량을 최적화했으며, DNN과 SNN을 상보적으로 활용해 모두 효율적으로 신경망 연산을 처리할 수 있는 AI 반도체용 통합 코어 구조를 취한다.

또 SNN 처리에 소모되는 전력을 줄이기 위해 출력 스파이크 추측 유닛을 개발했으며, 거대 언어 모델의 파라미터를 효과적으로 압축하기 위해 빅-리틀 네트워크 구조와 암시적 가중치 생성기법, 그리고 부호 압축까지 총 세 가지 기법을 사용했다.

이를 실제 활용한 결과 GPT-2 거대 모델의 708M개에 달하는 파라미터를 191M개로 줄였으며, 번역을 위해 사용되는 T5 모델의 402M개의 파라미터 역시 같은 방식을 통해 76M개로 줄일 수 있었다.

연구팀은 또 세 가지 압축 기법 적용을 통해 언어 모델의 파라미터를 외부 메모리로부터 불러오는 작업에 소모되는 전력을 약 70% 감소시켰다.

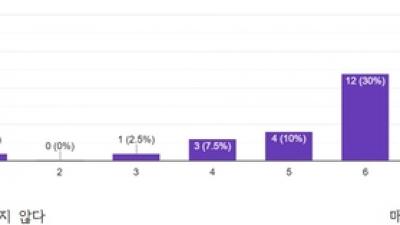

그 결과 상보형-트랜스포머는 전력 소모를 엔비디아 A100 대비 625배만큼 줄이면서도 GPT-2 모델을 활용한 언어 생성에는 0.4초의 고속 동작이 가능하며, T5 모델을 활용한 언어 번역에는 0.2초의 고속 동작이 가능했다. 생성된 문장 또한 사람이 읽기에 어색함을 느끼지 않을 수준으로 정확도를 확보했다.

연구팀은 이번 연구성과가 모바일 장치 등 에너지 제약이 높은 환경에서도 정확하게 LMM을 구동할 수 있어 온디바이스 AI 구현을 위한 최적의 기술이라고 설명한다.

유회준 KAIST 전기 및 전자공학부 교수는 “이번 연구는 기존 AI 반도체가 갖는 전력 소모 문제를 해소했을 뿐만 아니라 GPT-2와 같은 실제 LMM 응용을 성공적으로 구동했다는데 큰 의의가 있다”며 “향후 뉴로모픽 컴퓨팅을 언어 모델에 국한하지 않고 다양한 응용 분야로 연구범위를 확장할 것이며, 상용화에 관련된 문제점들도 파악해 개선할 예정”이라고 말했다.

한편 이번 연구는 지난달 19~23일 미국 샌프란시스코에서 열린 국제고체회로설계학회(ISSCC)에서 발표 및 시연됐다.

이인희 기자 leeih@etnews.com