IMEC이 2013년 1분기에 14나노 공정 디지털반도체(로직) 패턴 개발을 완료한다. 10나노와 7나노를 거쳐 2019년에는 5나노 로직 생산에 들어갈 계획이다.

유럽 최대 나노·반도체 연구기관인 IMEC이 10나노 이하 기술 로드맵을 제시함에 따라 세계 반도체 업계 간 미세공정 경쟁도 더욱 뜨거워질 전망이다.

IMEC은 11일(현지시각) 벨기에에 위치한 IMEC에서 ‘ITF(IMEC Technology Forum) 프레스 초청 행사’를 개최하고 이 같은 내용의 반도체 미세 공정 로드맵을 발표했다.

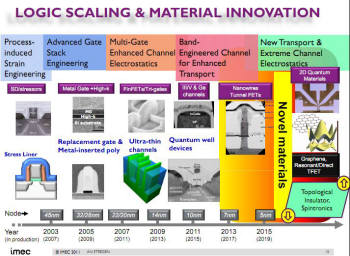

IMEC은 로직과 메모리 개발 로드맵에 대해 각각 제시했다. 반도체업계는 45나노 이후 새로운 방식을 도입해 회로 미세화를 진전시켜왔다. 32/28나노 로직에서는 메탈 게이트를, 22/20나노부터 14나노에서는 인텔 트라이게이트와 같은 멀티게이트를 도입해 기술 장벽을 극복했다.

IMEC은 14나노에 이은 10나노에서는 인듐·갈륨·비소 등 원소를 게르마늄에 넣음으로써 발전시킬 수 있다고 설명했다. IMEC은 14나노 로직 개발을 위해 2012년부터 극자외선(EUV)를 사용할 계획이다. 10나노 생산 시점은 2015년이 될 것으로 전망했다.

이후 7나노와 5나노는 탄소나노튜브(CNT)와 같은 나노선(와이어) 등장을 예고했다. 5나노 이하부터는 그래핀과 같은 혁신적인 재료를 통해서만 해결할 수 있을 것으로 예측했다. 7나노는 2017년, 5나노는 2019년이 되어야 실제 생산에 접목할 수 있을 것으로 바라봤다.

메모리는 낸드와 D램이 각각 다른 방향으로 발전할 것이라며 차별화된 기술개발 방침을 설명했다. 낸드플래시에서는 3D 아키텍처와 R램 전략으로 이원화한다. D램에서는 셀 저장 확장과 혁신적인 새로운 메모리 전략에 집중키로 했다.

IMEC은 20나노 낸드는 플로팅게이트를 통해 미세화가 진행됐지만 17나노부터는 회로를 수직으로 세우는 3D 아키텍처가 해답이 될 수 있다고 소개했다. 이어 14~11나노 낸드플래시는 수직 층을 더 높임으로써 미세화를 이루게 된다. 11나노 이하에서는 완전히 새로운 반도체 R램이 대체할 것이라고 전망했다. D램도 16나노 이하부터는 혁신적인 소재가 도입 만이 해결할 수 있다고 설명했다.

웨이퍼 사이즈 혁신에 대한 로드맵도 발표했다. 현재 반도체는 최대 300㎜ 웨이퍼에서 생산된다. 생산성을 높이기 위해서는 웨이퍼 크기를 확대해야 한다. IMEC은 450㎜ 웨이퍼를 2015년 중순까지 테스트를 마치고 2014년 중순부터 2017년까지 프로세스를 개발할 계획이다. 450㎜웨이퍼를 통한 시제품은 2015년 말부터 생산할 수 있을 것으로 기대했다.

루크 반 덴 호브 IMEC CEO는 “반도체 생산성을 높이는 투자에는 타이밍이 매우 중요하다”며 “IMEC은 450㎜를 어떻게 도입할 것인지에 대한 로드맵을 이미 세웠다”고 말했다.

루벤(벨기에)=

문보경기자 okmun@etnews.com