세계 최초 웨어러블 기기용 확대 도입

전작 대비 CPU 20%·그래픽 10배 향상

FO-PLP 등 첨단 패키징 기술 총집약

SoC 기술력 입증…시장 주도권 확보

삼성전자가 11일 출시하는 스마트워치 '갤럭시워치4'에 극자외선(EUV) 공정을 적용한 5나노(㎚) 기반 프로세서를 탑재한다. 웨어러블 기기용 프로세서에 EUV 공정을 활용한 건 삼성전자가 최초다. 초미세 회로를 그릴 수 있는 EUV 공정을 웨어러블용 프로세스까지 확대 적용, 첨단 시스템반도체 시장 주도권을 잡겠다는 포부로 읽힌다.

삼성전자는 최신 5나노 공정 기반의 웨어러블용 프로세서 '엑시노스 W920'을 출시했다고 10일 밝혔다.

엑시노스 W920은 웨어러블용 프로세서로는 처음으로 EUV 공정이 적용됐다. 최근 14나노급 D램 메모리(DDR5)에 EUV 공정 레이어를 1개에서 5개로 확대한다고 발표한 삼성전자는 웨어러블용 프로세서까지 EUV를 적용, 첨단 미세공정 활용 범위를 대폭 넓혀가고 있다.

신제품은 최신 설계 기술을 통해 기존 제품 대비 성능과 전력 효율을 한층 더 끌어올렸다. 엑시노스 W920은 2018년 출시한 엑시노스 9110 대비 중앙처리장치(CPU) 성능은 20%, 그래픽 성능은 최대 10배 이상 향상됐다. CPU와 그래픽처리장치(GPU) 코어는 ARM의 저전력 '코어텍스 A55'와 '말리-G68'을 각각 탑재했다.

저전력 디스플레이용 '코어텍스-M55'도 추가 탑재했다. '올웨이즈온디스플레이(AOD)' 모드에서 프로세서의 디스플레이 구동 전력 소모를 최소화하기 위해서다. AOD는 전체 화면을 켜지 않고 시계·알람·부재 중 전화 등 간단한 내용을 상시 확인할 수 있는 기능이다.

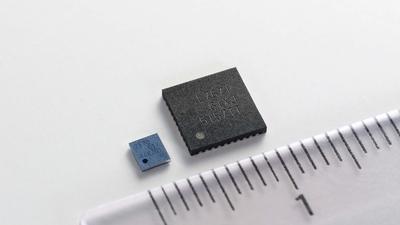

웨어러블용 초소형 패키지를 구현하기 위한 최첨단 패키징 기술을 적용한 것도 돋보인다. 팬아웃패널레벨패키징(FO-PLP)이 대표적이다. FO-PLP는 인쇄회로기판(PCB) 기판 없이 입출력(I/O)단자 배선을 칩 바깥으로 빼내 방열과 전기적 특성을 개선한 첨단 패키징 기술이다. 사각형 패널 위에서 패키징해 반도체 칩 크기를 줄이고 생산량도 늘릴 수 있다. 삼성전자는 2018년부터 웨어러블용 프로세서에 FO-PLP 기술을 적용하고 있다. 또 애플리케이션프로세서(AP)와 D램, 낸드플래시, 데이터저장용 내장 메모리반도체(eMMC), 전력관리반도체(PMIC)까지 하나의 패키지에 담는 첨단 패키징 기술 SIP-ePOP 기술도 적용했다. 모두 웨어러블 기기 소형화에 필수적이다.

삼성전자가 EUV를 포함, 첨단 패키징 기술을 엑시노스 신제품에 집약함으로써 일각에서 제기된 삼성전자 시스템온칩(SoC) 경쟁력에 대한 우려를 해소할 것으로 보인다.

지난달 삼성전자 2분기 실적 발표에서 조장호 삼성전자 시스템LSI사업부 상무는 “엑시노스를 향한 시장 우려를 잘 이해하고 있다”며 “신규 GPU 설계자산(IP) 도입으로 성능과 전력 효율성을 개선하는 등 엑시노스 경쟁력 향상을 위해 다방면으로 노력하고 있다”고 밝힌 바 있다. 엑시노스 W920을 통해 삼성전자 SoC 경쟁력의 건재함을 입증하려는 것으로 풀이된다.

엑시노스 W920은 삼성과 구글이 개발한 신규 통합 플랫폼 '웨어 OS'를 지원한다. 삼성 갤럭시 Z폴드3·플립3와 함께 공개되는 차세대 스마트워치 갤럭시 워치4 시리즈에 탑재된다.

조 상무는 “스마트워치는 단순 기기가 아닌 사용자 건강과 재미를 책임지는 핵심 웨어러블 기기로 발전하고 있다”면서 “엑시노스 W920을 탑재한 차세대 웨어러블 기기는 끊김 없는 롱텀에벌루션(LTE) 통신은 물론, 시각적으로 뛰어난 인터페이스와 빠른 사용자경험을 제공할 것”이라고 밝혔다.

권동준기자 djkwon@etnews.com