‘무어의 법칙’이 오는 4월 19일 탄생 50주년을 맞는다. 2년마다 칩의 집적도가 두 배 이상 높아진다는 무어의 이론은 50년이 지난 지금까지 세계 반도체 시장을 움직이는 가장 강력한 법칙으로 작용한다. 데이터 저장 용량을 지속적으로 높이되 크기와 발열은 줄이고 전력 효율성을 높이는 반도체 기술 혁신의 대표적인 지표다.

◇트랜지스터 집적화 기술에서 찾은 혁신

인텔 공동 창업자인 고든 무어는 지난 1965년 4월 일렉트로닉스매거진에 ‘집적회로에 더 많은 부품 채워넣기(Cramming more components onto integrated circuits)’라는 글을 기고했다. 이 글에서 무어는 반도체 집적화 기술이 전자학의 새로운 미래를 열어갈 것이라고 언급했다.

특히 무어는 원가 절감이 집적화의 최대 매력 중 하나이며 집적화가 빨라질수록 가격이 급격히 떨어진다는 집적화와 제조 원가의 상관관계를 제시했다.

무어는 당시 “부품 제조비용을 최소화하는 복잡성은 해마다 약 2배로 증가했고 이 현상을 유지하는 것이 확실하다”고 언급했다. 또 “적어도 앞으로 10년 동안 거의 일정한 비율을 유지할 수 있지만 장기적으로는 증가율이 조금 불확실하다”며 “1975년까지 최소 비용으로 얻을 수 있는 집적 회로의 부품 수는 6만5000개에 이를 것이고 그만큼의 대규모 회로를 1개 회로판 위에 구축할 수 있다고 믿는다”고 밝혔다.

무어는 1970년이 되면 컴포넌트 당 제조원가가 1965년 대비 10분의 1이 될 것이라고 예측했다. 무어의 법칙 원조인 ‘최소 부품 비용의 집적도는 약 1년에 2배 비율로 높아졌다’는 표현을 남겼다.

이후 무어는 10년 후인 1975년에 ‘약 2년마다 칩의 집적도는 2배씩 증가한다’고 자신의 이론을 수정했다. 당시 인텔 중역이었던 데이비드 하우스가 무어의 이론을 기반으로 ‘칩의 집적도는 18개월마다 2배씩 높아질 것’이라고 말하기도 했다.

당시 무어가 반도체 성능이 기하급수적으로 증가한다고 예측한 것은 현실 가능성이 없는 내용으로 치부됐다. 무어 자신도 “당시 누가 맞장구를 쳐줄 것이라고 생각하지 않았다”고 밝힐 정도였다.

◇50년간 이어진 데이터 용량·성능과의 싸움

무어의 법칙은 비용을 줄이되 더 높은 성능의 칩을 제공하는 큰 원칙으로 자리 잡았다. 인텔은 4~5년 걸리는 제품 출시 기간을 절반으로 줄이며 차세대 제품을 빠르게 공급해 새로운 시장을 만드는데 성공했다.

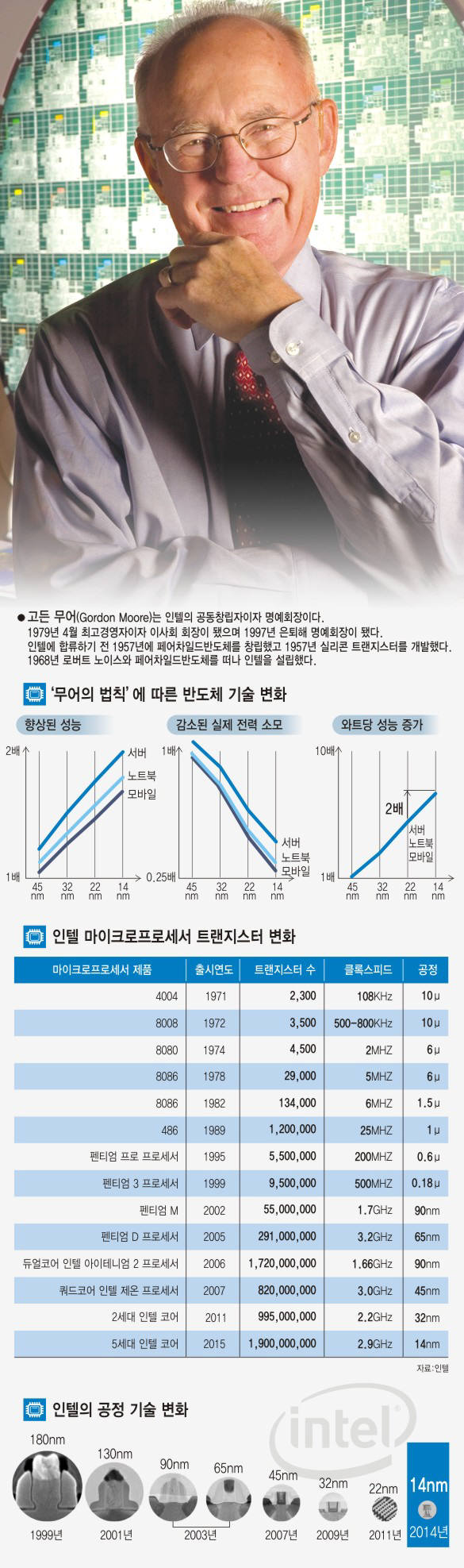

실제로 인텔은 트랜지스터 집적도를 빠르게 높이며 세계 반도체 업계 선두 입지를 확고히 했다. 1971년에 선보인 4004 프로세서의 경우 트랜지스터 수는 2300개에 불과했지만 2015년 출시한 5세대 인텔코어 프로세서는 19억개 트랜지스터를 집적했다. 82만6000배가량 트랜지스터 수가 증가한 셈이다.

데이터 용량과 처리 속도를 높이기 위해 인텔은 다양한 기술을 시도했다. 2005년 처음 선보인 듀얼코어 프로세서인 펜티엄 D 프로세서의 경우 프로세서 1개에 2개 코어를 집적한 새로운 기술로 업계 눈길을 집중시켰다. 펜티엄 D 프로세서는 듀얼코어를 대중화한 핵심 제품군으로 꼽힌다.

이후 1개 CPU에 코어를 4개 탑재한 쿼드코어, 코어 8개를 탑재한 옥타코어로 빠르게 기술이 발전했다. 이제는 PC뿐만 아니라 스마트폰도 멀티코어를 채택할 정도다.

반도체 회로 선폭을 줄여 웨이퍼 당 더 많은 칩을 설계할 수 있도록 공정 기술도 함께 발전했다. 회로 선폭이 줄어들수록 누설 전류가 늘어나고 발열이 심해지는 문제를 해결하기 위해 소재와 설계를 바꾸는 노력도 함께 진행됐다.

인텔은 1999년 180나노미터(㎚), 2001년 130나노, 2003년 90나노, 2005년 65나노, 2007년 45나노, 2009년 32나노, 2011년 22나노, 2014년 14나노로 기술 진화를 거듭했다. 공정을 미세화할수록 부딪치는 기술 장벽을 새로운 물질과 설계 방법으로 돌파했다.

90나노는 변형 실리콘을 적용해 트랜지스터 성능을 높였다. 45나노 공정에는 하이케이메탈게이트를 적용했다. 22나노 공정에서는 전류의 흐름을 조정하는 게이트를 평면(플래너) 구조에서 세 방향으로 구성한 트라이게이트 트랜지스터 구조로 변경해 집적도를 높였다.

14나노에서는 22나노보다 트라이게이트 구조를 개선해 핀의 간격과 게이트 길이를 줄여 트랜지스터 밀도를 한층 높인 핀펫(FinFET) 기술을 선보였다. 핀의 간격은 22나노에서 60나노였으나 14나노에서 42나노 길이로 30% 줄였다. 게이트 길이 역시 90나노에서 70나노로 22% 짧아졌다.

인텔은 14나노 칩을 상용화한데 이어 2015년 이후에는 10나노, 7나노 등으로 미세 공정을 실현해 나갈 방침이다. 10나노 제품은 2017년경 등장할 것으로 예측된다. 14나노 핀펫 공정 제품을 최초로 상용화한 데 이어 10나노, 7나노 제품에 대한 기술 개발이 상당한 수준이어서 세계 반도체 업계 선두 자리를 유지해나갈 수 있다는 자신감이 크다.

◇고든 무어는 누구?

고든 무어(Gordon Moore)는 인텔의 공동창립자이자 명예회장이다. 1979년 4월 최고경영자이자 이사회 회장이 됐으며 1997년 은퇴해 명예 회장이 됐다. 인텔에 합류하기 전 1957년에 페어차일드반도체를 창립했고 1957년 실리콘 트랜지스터를 개발했다. 1968년 로버트 노이스와 페어차일드반도체를 떠나 인텔을 설립했다.

배옥진기자 withok@etnews.com