와카바야시 도쿄공업대 교수 주장

한 자릿수 nm까지 기술 진화했지만

글로벌 둔화 추세에 양산도 어려워

칩렛·3차원 적층 등 신기술 주목

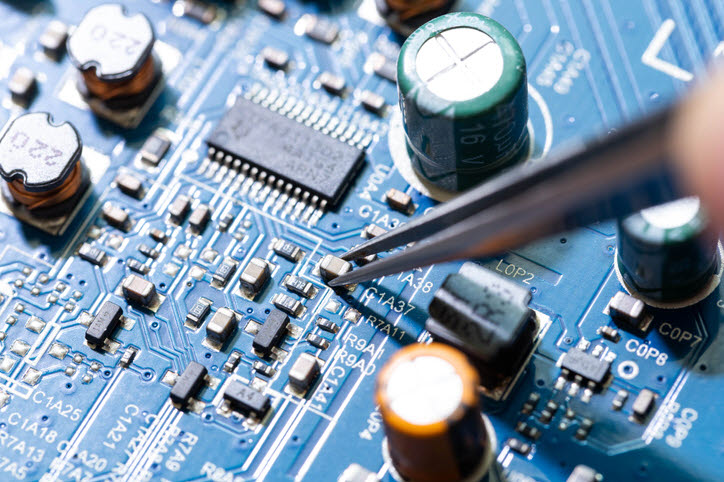

글로벌 반도체 기업들이 '미세화 공정' 둔화 추세에 따라 신기술 확보 경쟁에 나설 것이라는 주장이 제기됐다. 한국과 대만을 중심으로 반도체 선폭 미세화가 한계 수준까지 진행되면서 차세대 시장을 이끌 새로운 제조 기술이 핵심 경쟁력으로 부상하고 있기 때문이다.

와카바야시 히토시 도쿄공업대 월드리서치허브이니셔티브(WRHI) 교수는 7일 니혼게이자이신문(닛케이) 인터뷰에서 이 같은 내용을 강조했다.

NEC, 소니 등에서 근무한 그는 현재 한자리 수 나노미터(㎚)까지 진행된 미세화 공정이 곧 한계에 이를 수 있다며 반도체 기업이 기술 변화에 대비해야 한다고 조언했다.

반도체 회로 선폭이 좁을수록 더 작은 마이크로칩을 제조할 수 있어 동일 웨이퍼 기준 생산성이 높아진다. 더 높은 에너지 효율과 고성능 제품 생산도 기대할 수 있다. 하지만 어렵게 기존보다 좁은 선폭을 구현해도 이를 대량 생산하기 어렵다는 것이 또 다른 장애물이다.

와카바야시 교수는 “삼성전자가 개발한 4㎚ 제품이 삼성 갤럭시 스마트폰에, TSMC의 5㎚ 제품이 애플 아이폰·맥북에 탑재됐다”면서 “(미세 선폭) 양산기술을 확보하기 어려웠기 때문에 일본은 물론 미국 인텔까지 떨어져 나가면서 (삼성과 TSMC의) 과점화가 진행됐다”고 진단했다.

그는 앞으로 삼성전자와 TSMC가 고성능 반도체를 생산하는 데 활용하는 양산기술이 업계에서 조명받을 것이라고 예상했다. 삼성은 3㎚, TSMC는 2㎚에서 과거와 다른 '나노시트' 구조를 활용할 계획이다.

삼성과 TSMC는 각각 4㎚, 3㎚ 제품 트랜지스터에 '핀펫(FinFET)'이라는 입체 구조를 적용했다. 아직 나노시트 양산기술이 정립되지 않은 상황에서 각 기업이 어떻게 생산할지에 관심이 쏠린다.

와카바야시 교수는 1㎚ 전후 제품까지 미세화 공정이 가능할 것이라고 내다봤다. 하지만 반도체 자체 기능을 고려하면 선폭 미세화 이외 성능 개선 기술이 등장할 것이라고 예상했다.

그는 “회로 선폭이 5㎚를 밑돌면 '터널효과'라는 양자역학 현상이 일어나기 때문에 반도체로서 기능하지 못하게 된다”면서 “트랜지스터를 2층으로 쌓아 성능을 높이는 등 다양한 방안이 검토되고 있다”고 설명했다.

닛케이는 앞으로 글로벌 반도체 산업에서 선폭 미세화 진행 속도가 둔화할 가능성이 있다고 전망했다. 이에 따라 반도체칩을 여러 개 붙여 미세화·소형화 한계를 극복하는 '칩렛'이나 칩을 위로 쌓아 단위 면적당 기능을 높이는 3차원 적층 기술 등이 주목 받고 있다고 설명했다. 또 앞으로 구글이나 애플처럼 글로벌 정보기술(IT) 기업들이 칩 자체 개발에 나설 가능성이 있다고 덧붙였다.

윤희석기자 pioneer@etnews.com