인텔이 내년 상용화할 2나노미터(㎚) 수준 인텔 20A 공정에 파워비아 기술과 리본펫을 적용, 반도체 경쟁력을 강화한다.

나승주 인텔코리아 상무는 13일 서울 삼성동 코엑스에서 열린 ‘2023 글로벌 소부장 테크페어’에서 “세계 각지에 인텔 공장 확대와 중앙처리장치(CPU)를 제외한 반도체 일부 타사 파운드리 이용, 세계 톱 클래스 인텔 파운드리 서비스 지원 등을 골자로 한 종합반도체기업(IDM) 2.0 전략을 바탕으로 반도체 업계 리더십을 공고히 하겠다”면서 이같이 밝혔다.

파워비아는 인텔 후면 전력 공급 기술이다. 반도체 업계에서 인텔이 처음 개발한 기술이다. 웨이퍼 뒷단에 전력 공급으로 신호와 전력 배선을 분리했다. 현재 회로가 그려진 웨이퍼 전면에 배선을 적용해 전력을 공급하고 있지만 인텔은 파워비아로 테스트칩 후면에서 전력을 공급, 전력 효율성을 높이고 반도체 성능을 높이는 데 성공했다.

나 상무는 인텔 4 공정(7㎚)으로 생산한 테스트칩에 파워비아를 적용한 테스트 결과, 반도체 셀 밀도를 높여 비용을 절감할 수 있고 보다 적은 전력으로 높은 주파수를 얻고 전력 소모도 줄일 수 있었다고 설명했다.

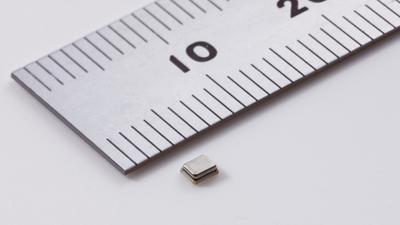

반도체 칩 내 저전력·고효율을 담당하는 E코어 성능이 6% 이상 향상됐고 전압 강하는 30% 이상 개선됐다. 단위 면적당 셀 밀접도를 높여 칩(다이) 90% 이상을 활용할 수 있게 했고 전력 관련 신뢰성 위반 가능성은 0%로 확인되는 성과를 얻었다. 반도체 칩 크기도 세로 길이가 30㎚ 줄어들어 웨이퍼당 더 많은 칩 생산이 가능해진다.

인텔은 내년 상반기 인텔 20A 공정부터 파워비아를 적용할 계획이다. 하반기에는 1.8㎚ 수준 인텔 18A 공정에도 적용한다는 구상이다.

차세대 트랜지스터 구조 ‘리본펫’도 파워비아와 함께 적용한다. 리봇펫은 삼성전자가 업계 최초로 양산한 게이트올어라운드(GAA)의 인텔 브랜드다.

나 상무는 “인텔은 2.5D·3D 패키징 기술과 하이브리드 본딩은 물론, 칩과 칩 사이를 연결하는 브릿지 다이 고도화, 유리기판 도입과 패키지 광학기술 업그레이드로 첨단 패키징 기술을 지속 선도할 계획”이라며 “파워비아와 같은 신기술 개발, 새로운 소재 활용을 통한 반도체 혁신과 2030년 패키지당 1조개의 트랜지스터를 집적하는 등 ‘무어의 법칙’이 지속 유지되도록 할 것”이라고 말했다.

박종진 기자 truth@etnews.com