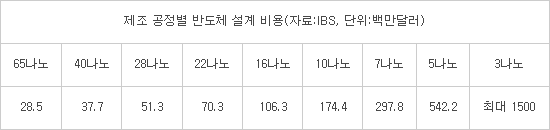

관련 통계자료 다운로드 제조 공정별 반도체 설계 비용

관련 통계자료 다운로드 제조 공정별 반도체 설계 비용 삼성전자가 2020년 3나노 파운드리 생산 공정을 개발한다는 계획을 세운 가운데 해당 공정 노드 칩 설계 비용이 최대 1조7000억원(15억달러)에 이를 것이라는 분석이 나왔다. 칩 설계 비용은 기하급수적으로 늘어나지만 3나노로 공정을 전환했을 때 기대되는 전력효율과 성능 향상 이점은 비용만큼 크지 않다는 것이 전문가 분석이다. 이 같은 비용을 감수하면서 3나노 칩을 설계할 수 있는 회사가 몇 손가락 안에 꼽을 정도로 적다는 점에서 파운드리 업계 고민이 깊어지고 있다.

17일 반도체 공정 분석 전문업체인 인터내셔널비즈니스스트래티지(IBS)는 3나노 공정 칩 설계 비용이 최소 5500억원에서 최대 1조7000억원까지 들어갈 것이라고 분석했다. 비교적 설계가 복잡한 그래픽처리장치(GPU) 등을 설계할 때 최대 비용이 들어간다고 IBS는 설명했다. 이 회사 자료에 따르면 28나노 평면형 칩 설계 비용은 평균 5130만달러다. 핀펫 기술이 적용되는 7나노 칩은 2억9780만달러로 설계 비용이 6배 가까이 껑충 뛰어오른다. 반도체 칩 설계에는 설계자산(IP) 검증, 아키텍처 설계, 검사, 물리검증, 소프트웨어 내장, 시제품 제작 등에 비용이 들어간다.

업계에선 이러한 이유 때문에 주요 팹리스 회사 대부분이 TSMC 16나노 핀펫이나 삼성전자 14나노 핀펫 공정을 오랫 동안 활용하게 될 것이라고 관측하고 있다.

파운드리 업계도 비용 때문에 고민이다. 3나노 기술 구현이 쉽지 않기 때문이다. 삼성전자는 3나노 공정에서 GAAE(Gate-All-Around Early), GAAP(Gate-All-Around Plus) 기술을 처음 적용한다. 삼성전자는 이 기술의 독자 명칭을 MBCFET(Multi Bridge Channel FET)이라고 정했다. 전류가 흐르는 게이트 통로를 기존 각형 핀펫 구조에서 모든 면에 두는 것이 핵심이다. 핀펫은 3개 면에서 전류가 흘렀지만, GAA는 게이트를 감싸는 모든 면으로 전류를 흘릴 수 있다. 전류가 흐르는 통로가 커지면 그 만큼 성능이 좋아진다.

삼성전자의 MBCFET 기술은 미국 IBM, 글로벌파운드리(GF)와 공동 개발한 나노시트 기반이다. 핀펫은 물고기 지느러미처럼 게이트를 수직으로 세웠지만, 나노시트 기반 GAA는 나노시트 기반 게이트를 가로로 눕히고 위로 몇 개씩 쌓는 형상을 갖고 있다. 이 같은 게이트 구조를 만들기 위해 패턴 형성, 증착, 식각, 계측 공정의 혁신은 물론 원치 않는 저항을 없애기 위해 인터커넥트 재료로 구리 대신 코발트나 루테늄 같은 신 재료를 도입해야 한다.

업계 관계자는 “3나노 GAA 공정 개발과 이에 맞는 칩 설계는 막대한 비용을 쏟아 부으면 어떻게든 되겠지만 문제는 들인 돈 만큼 가치를 할 수 있느냐가 될 것”이라면서 “해당 공정을 활용할 수 있는 회사도 퀄컴, 엔비디아, 애플 정도 밖에 없다는 점도 걸림돌”이라고 말했다.

한주엽 반도체 전문기자 powerusr@etnews.com