<경종민> KAIST 전기.전자공학과 교수 <>75년 서울공대 전자공학과 졸업(학사) <>77~81년 한국과학기술원 전기및 전자공학과 졸업(석사, 박사)<>81~83년 미국 AT&T 벨연구소 근무 <>83년~현재 한국과학기술원 전기및 전자공학과 교수<>89~89년 독일 칼스루 헤공대 훔볼트재단 지원 방문교수 반도체 칩중 부가가치가 크고 설계하기도 복잡한 것이 마이크로프로세서일것이다. 복잡미묘한 최신 컴퓨터구조의 변혁이 마이크로프로세서 칩안에서이루어지며 설계에 필요한 셀과 종류도 매우 다양할 뿐 아니라 컴파일러 마 이크로코드 등 소프트웨어 이슈와도 매우 관련이 깊기 때문에 쉽게 덤벼들기 어려운 기술분야가 바로 마이크로프로세서라고 할 수 있겠다.

CISC마이크로프로세서 시장에서 AMD, 사이릭스, 넥스젠 등 호환 칩 업체의 맹추격을 받고 있는 인텔은 더 좋은 성능의 칩을 발표함으로써 경쟁회사들을 좌절시키고 프로세서시장을 완전히 독점하겠다는 의도로 계속 새로운 x86 버전을 개발하고 있다. CISC의 x86독주와는 다르게 RISC 마이크로프로세서 는 춘추전국시대를 방불케 할 만큼 SPARC, MIPS, PA-RISC, 알파 등 다양한 프로세서가 워크스테이션 시장을 노리고 있다. IBM과 모토롤러, 그리고 애플 은 x86 아키텍처와 PC시장에서 정면 대결하기 위한 RISC 마이크로프로세서파워 PC를 만들었다. 인텔의 x86칩 계열은 기존 소프트웨어와의 호환성 유지를 위해 하드웨어의 많은 부분에서 비능률적 요소가 축적되었으나 마이 크로프로세서 시장에서는 바로 그 소프트웨어 때문에 왕좌를 굳건히 지키고있는 것이다.

인텔 마이크로프로세서 호환칩 개발 경쟁 x86 응용프로그램이라는 거대한 사용자 인프라에 대한 지원을 포기하지 않을 수 없기 때문에 모든 CPU회사는 x86 명령어를 보다 빨리 수행하거나 에뮬레이션하는 기법을 찾아내기 위해 노력하고 있는데 프로그램 수행에는 인텔의 펜티엄, 넥스젠의 Nx586, 사이릭스의 M1, AMD의 K5칩이 동일한 수행 결과를 보장하지만 전혀 다른 마이크로 구조로 서로 다른 성능을 발휘하고 있다. 사이릭스는 올해초 M1이라는 펜티엄급의 프로세서 아키텍처를 발표하였다. M1은 인텔의 펜티엄과 유사한 아키텍처를 유지하며 파이프라인을 개선하여 성능을 향상시키는 방향을 택하였다. M1은 인텔의 펜티엄에 비해 정교하지만복 잡한 두개의 파이프라인을 가지고 있다. 각각 "X-파이프" Y-파이프 라고불리는 이 두개의 파이프는 펜티엄보다 두 단계가 많을 뿐 아니라 파이프 라인 상의 거품을 없애기 위한 기능을 가지고 있다. 32개의 GPR(General Purpose Register)를 레지스터 Renaming으로 사용하며 분기 예측기능과 추리 수행기능을 가지고 있으며, 인텔의 펜티엄보다 슈퍼스칼라 수행의 제약이 적기 때문에 보다 나은 성능을 보일 것으로 예상된다.

넥스젠이 발표한 Nx586은 80x86명령어 집합을 지원하면서 마이크로 아키텍처는 CISC/RISC를 혼합한 아키텍처를 가지고 있다. Nx586은 x86명령 어를 메모리에서 가져다가 해석한 후 이를 RISC타입의 명령어(RISC86이라고 부름)로 변환시켜 이를 RISC-like 코어에서 수행시킨다. 넥스젠은 인텔이 펜 티엄에서 택한 방향과는 다른 방향의 접근을 하였는데 인텔이 FPU를 강화한 데 비해 정수연산을 중시하였다. Nx586은 내부에 FPU가 없으며 이를 따로Nx587이라는 보조 프로세서를 통하여 지원하고 있다. 대신 FPU에 사용될면적을 캐시에 할당하여 펜티엄에 비해 2배인 32KB의 캐시를 가지고 있다.

또한Nx586은 L2 캐시 컨트롤러를 내장하고 있으며, 이는 L2버스를 통하여L2캐시와 정보를 주고받기 때문에 외부 어드레스/데이터 버스와의 충돌이 발생하지 않는다.

AMD는 인텔과의 오랜 분쟁으로 인한 복사업체라는 오명을 씻기 위하여 지난9 2년부터 K5를 연구하였다. 그 결과 K5는 인텔 펜티엄과는 전혀 다른 아키텍처를 가진 독자적인 프로세서로 모습을 나타내었다. K5는 Nx586과 비슷한C ISC/RISC 혼합형의 아키텍처로 4-issue 슈퍼스칼라 구조로 되어있다. x86 명령어들은 "R-ops"라고 불리는 RISC-like명령어로 나누어져 각각의 연산장치에서 수행된다. K5는 명령어 캐시를 특별하게 설계하여 명령어를 캐 시에 읽어들이는 단계에서 미리 프리-디코딩을 행하게 된다. 이러한 프리-디코딩은 명령어의 디코딩 시간을 줄일 수 있게 해 4개까지의 명령어를 동시에 이슈할 수 있게 해준다.

AMD 최초로 독자적인 마이크로 코드를 사용한 K5는 현재 발표된 펜티엄 급의 호환 프로세서들 중에서는 가장 앞선 성능을 가진 것으로 생각된다.

등장을 앞두고 있는 P6 펜티엄은 슈퍼스칼라를 도입했지만 초보적인 수준에 불과했다. P6은 부동소수점 처리 유닛을 보다 향상시켜서 정수처리유닛과 마찬가지로 부동 소수점 처리유닛도 2개를 두어 완전한 슈퍼 스칼라 동작을 하게 한다. 그리고 무엇보다 현재 인텔 x86계열 아키텍처의 최대 약점인 내부 레지스터의 확장을 고려하게 될 것이다. 스파크나 MIPS의 성능이 뛰어난 이유 중 하나는 내부에수십 수백개의 레지스터를 갖고 있기 때문에 외부 메모리 사이클에 의한 시간지연을 최소화시켜주는 것인데 x86계열에서는 고작해야 8개의 범용 레지스터를 갖고 있을 뿐이다. 이를 극복하기 위해 레지스터 Renaming기법이 도입될 것으로 기대된다. 그리고 P6에서도 펜티엄까지의 순차적인 명령어 처리에서 벗어나 Out-of-order명령어 처리를 가능하게 하는 아키텍처를 도입 할 것으로 보인다.

P6은 1백33MHz클록 주파수에서 2백50~3백MIPS정도의 성능으로 현재 펜 티엄보다 2~3배의 스피드를 낼 수 있을 것이고, 0.4㎙공정으로 6백만 트랜지스터를 집적시킬 것으로 예상된다. 그리고 내부에는 2백56KB의 캐시를 내장하고 있으며 2차 버전에서는 그 크기를 5백12KB로 증가시킬 것으로 알려져 있다. 그밖에 PCI(Programmable C-ontrol Interrupt), APIC(Advan ced Programmable Interrupt Controller)를 내장하여 멀티프로세서를 위한캐 시 일관성 문제를 쉽게 처리해줄 것으로 예상된다.

RISC마이크로프로세서들의 춘추전국시대 현재 발표된 대표적인 RISC프로세서들은 다음과 같다. TI.LSI등의 SPARC, IBM.애플.모토롤러의 파워PC, 휴렛팩커드(HP)의 PA-R ISC, DEC의 알파, MIPS의 R4000, 모토롤러의 88000, 인텔의 i86 0, i960. 이중 한 두개의 RISC만 시장에서 살아남아 아직은 CISC계 열에서 강력한 아성을 구축하고 있는 인텔의 x86계열 아키텍처(결국은 펜티엄 와 경쟁하게 될 것이다. 윈도즈 및 네트워킹 기능의 도입으로 PC 성능 이 점점 고급화 되어가면서 워크스테이션과 PC의 구분이 모호해지고 있는추세속에 스팍과 파워PC가 펜티엄과의 가장 치열한 전쟁을 치르고 있다.

93년 데이터퀘스트의 조사에 의하면 MIPS와 스파크칩의 강세가 돋보이고파워PC와 PA-RISC의 시장점유율도 상당함을 알 수 있다. 94년 3월28일 자 "PC위크"에 의하면 현재까지 DEC의 알파 시스템은 2만5천대 정도밖에 팔리지 않았다고 하는데 의외로 DEC의 알파 시장은 크지 못함을 알 수있다. PA-RISC는 기존의 HP이외에도 히타치, OKI, 윈본드에서도제작되고 있다. MIPS칩 연합인 ACE가 사실상 해체되었고, 세미컨덕터 사는 파산했다. 스파크칩의 대부분은 후지쯔에 의해 만들어지는 반면 LSI 로직은 기존 스파크 칩 시장에서 점점 도태되어가고 있고, 필립스에서는 Emb edded 스파크를 공급하려 하고 있다.

슈퍼 스파크와 울트라 스파크는 TI에 의해 주도되어 나가고 있다. 현재 선사는 STB(Sun Technology Business)사를 새로 만들어 스파크칩 비즈니스 를 시작했다.

워크스테이션 시장에서는 기존 사용자를 다수 확보하고 있는 스파크와 MIPS가 계속 강세를 보이리라는 예측과 함께 파워PC가 우수한 성능과, 특히 PC시장에서의 x86구조 CISC의 강력한 경쟁자가 되리라는 예상이 강력하다. 현재 RISC칩은 파워PC620, R4000시리즈, 알파 스파크 V.

9,PA-RISC8000시리즈 모두 64비트 아키텍처로 가는 추세이며, 머지않아 1백28비트 버스가 등장할 것으로 예상된다. 슈퍼 스칼라와 슈퍼 파이프라 인 등의 기법은 이제 학술연구 대상이 아닌 마이크로프로세서의 필수적인 선택사항이 되었다.

시장에서 인정받지 못한 RISC칩은 자연도태되는데 AMD의 29000, 모토롤러 88 000이나 클리퍼 칩등이 그 예다. 단일 CPU로의 집적화 한계는 멀티프로세서 시스템의 등장을 필연적으로 가속시킬 것이다.

"21세기를 위한 Micro2000 마이크로프로세서는 P9나 P10이 될 것"이라고 인 텔의 컴퓨터 사업부 관리인 패트릭 젤시거는 예견한다. 하지만 인텔의 Micro 2000을 위한 구체적인 전략은 아직 밝혀지지 않았는데 지금까지의 프로세서 발전흐름을 고려할 때 약 5천만개이상의 트랜지스터를 한칩에 집적시킬 수있고 약 2백50MHz의 클록에서 동작하리라 예상된다.

인텔의 앤드루 그로브회장의 예언대로라면 트랜지스터 1억개의 칩을 Micro20 00으로 예견하고 있다. 처리속도도 2BIPS 정도가 될 것이다. Micro2000은 4개의 프로세서를 한 칩에 집적한(한 칩당 약4백만개의 트랜지스터를 집적)약 7백MIPS의 멀티프로세서시스템이 될 것이다. 또한 3차원 그래픽과 모델링, 그리고 시뮬레이션을 위한 i860같은 2개의 벡터 유닛을 내장하고 있으며하나의 유닛은 초당 10억개의 부동 소수연산이 가능하다. 그리고 자연과학과기 술적인 문제의 시각화를 위하여 3차원 고해상 컬러그래픽의 프린팅과 디스플 레이를 위한 그래픽 유닛을 포함하고 있고 약 2MB의 캐시를 내장하게 될 것이다. 인텔의 앞으로의 프로세서 디자인 방향은 하나의 칩안에 지금 우리가쓰고 있는 완전한 PC를 집적화시키는 것으로 가고 있는데 Micro2000은 외부적 기능(플로피디스크와 하드디스크를 위한 컨트롤칩, 메인메모리, 외부 컴퓨터와의 네트워크통신을 위한 칩)을 하나의 모듈로 집적할 것이고 또한 휴 먼 인터페이스를 위한 유닛을 포함할 것으로 알려져 있는데 약 2천만 트랜지스터가 휴먼 인터페이스와 음성입출력, 영상입출력등의 기능을 지원하면서PC 를 좀더 스마트하고 사용자가 사용하기에 편리하도록 할 것이다.

마이크로프로세서시장의 역할은 매우 복잡하다. 그저 기술적으로 우수하다고 해서 그냥 잘 팔리는 것도 아니고 전력소모, 소프트웨어 지원양상등의 면에서 여러 조건을 만족시켜야 한다. 우리나라는 어차피 반도체중심의 정보산업 기술분야에서 크게 투자, 성과를 기대하고 있으며 따라서 두각을 나타내지않으면 안되게 되었다.

마이크로프로세서는 반도체기술의 꽃과 같은 것이다. 이 꽃을 하나 피우려면 반도체 회로설계기술뿐 아니라 시스템 설계 및 스펙 검증기술, 컴파일러, OS등의 소프트웨어기술, 서브 미크론 공정기술과 라이브러리 및 CAD기술등이골 고루 발전해 있어야 한다. 따라서 떼돈을 당장 퍼붓는다고 되지도 않지만늦었다고 생각되는 이 시점에 바로 투자를 시작해야 한다. 내일을 위하여, 또 반도체산업뿐 아니라 주변의 컴퓨터.통신.가전.자동차 등 관련산업의 경쟁력 을 위해서 말이다. 혹자는 이렇게 말할지 모른다. 어떻게 감히 인텔 등수십 년간 그 일에만 전념해온 세계 굴지의 회사를 상대로 우리가 경쟁을 할수 있겠는가라고. 우리나라가 10여년전에 메모리사업에 뛰어들 때에도 전망은 매우 암울한 것이었으나 결국 세계 톱수준의 메모리 생산국이 된 것을 생각해 야 한다. 수요와 파급효과, 부가가치면에서 절대적 위치를 갖는 마이크로프로세서분야에 우리가 정면 승부를 거는 것은 어쩌면 이미 우리로서는 피할수 없는 선택으로 생각된다. 이를 위해서 표와 같이 하나의 마이크로프로세 서 칩을 개발하는데 칩설계기술뿐 아니라 이를 에워싸는 주변기술이 같이있어야 한다. 즉 시스템 설계와 분석 및 검증이 끝난 후에 칩으로 구현할 기능 이 결정되면 PCB등 주변 하드웨어와 시스템 소프트웨어 개발이 병행되어야한다. 물론 경쟁력있는 공정과 이를 활용할 수 있도록 라이브러리와 CAD 툴기 술이 뒷받침되어야 한다.

많이 본 뉴스

-

1

“저녁 대신 먹으면 살 쭉쭉 빠진다”···장 건강·면역력까지 잡는 '이것' 정체는?

-

2

“라면 먹을떄 '이것' 같이 먹지 마세요”…혈관·뼈 동시에 망가뜨려

-

3

의사가 극찬한 '천연 위고비'…“계란 먹고 살찌는 건 불가능”

-

4

배달 3사, 이번엔 '시간제한 할인' 경쟁…신규 주문 전환율 높인다

-

5

현대차, '더 뉴 그랜저' 디자인 공개…“新기술 집약”

-

6

中 BYD, 국내에 첫 하이브리드차 출시…전기차 이어 포트폴리오 다각화

-

7

'HMM 부산 이전' 李대통령 “약속하면 지킨다…이재명은 했다”

-

8

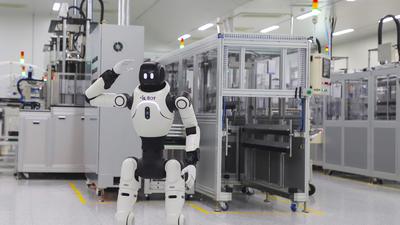

국내 최초 휴머노이드 로봇 쇼룸 문 연다…로봇이 춤추고 커피도 내려

-

9

삼성바이오 전면파업 이틀째…5일까지 총파업 강행

-

10

우리은행, 계정계 '리눅스 전환' 착수…코어 전산 구조 바꾼다

브랜드 뉴스룸

×

![]()