인텔이 고대역폭메모리(HBM) 대안으로 주목받는 'Z 앵글 메모리(ZAM)' 핵심 특허를 잇따라 확보했다. 인공지능(AI) 메모리 전력 소모와 발열을 획기적으로 줄일 수 있는 기술로, 지식재산권을 선점해 후발주자들의 추격을 가로막으려는 전략으로 분석된다.

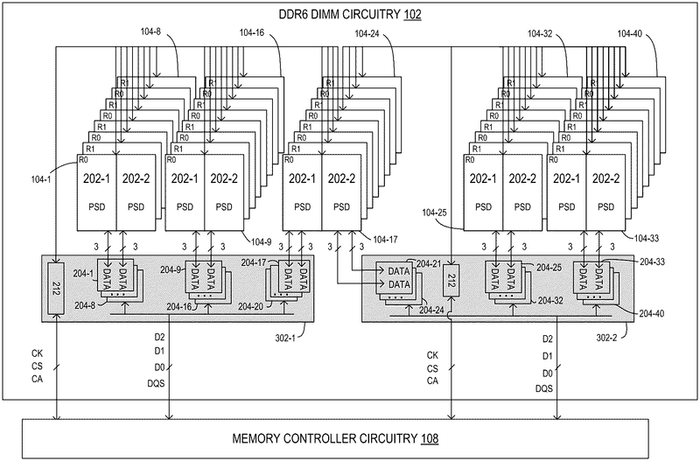

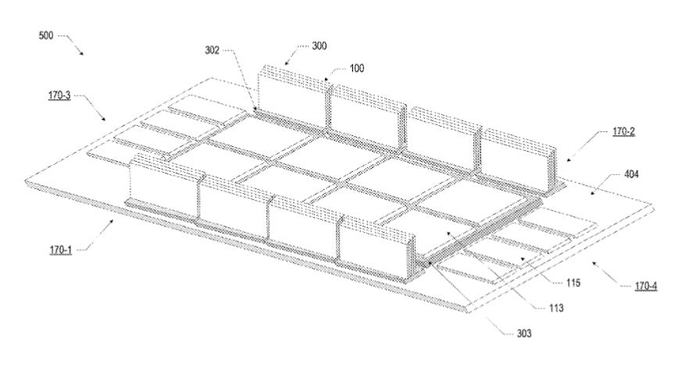

업계에 따르면, 인텔은 최근 미국에서 '의사 분할 다이 메모리 접근을 위한 방법 및 장치(US20260017215A1)' 특허를 공개했다. 인텔이 소프트뱅크와 공동 개발 중인 ZAM 구동에 대한 특허다.

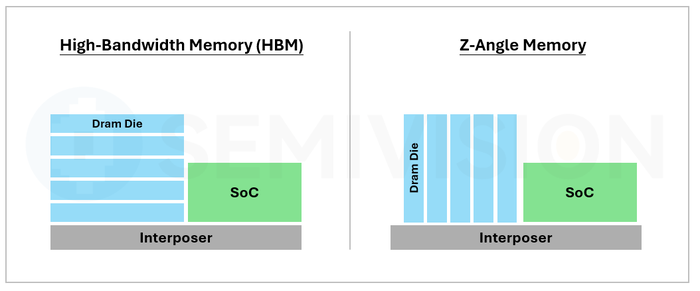

ZAM은 HBM처럼 D램을 수직으로 쌓아 구현하는 차세대 메모리다. HBM과 다른 점은 D램끼리 데이터를 주고받는 실리콘관통전극(TSV) 수를 대폭 줄였다는 것이다. 중심이 되는 TSV를 두고 사선 형태(Z)의 회로 배선으로 각 D램을 연결하는 구조다.

이번에 공개한 특허는 ZAM을 구성하는 각 D램 반도체(다이)를 한번에 구동하지 않고, 필요한 부분만 분할 활성화하는 것이 골자다. D램 적층구조의 가장 큰 취약점인 발열과 전력 소모를 해결하기 위한 개념이다. 또 회로 배선을 세밀하게 나누어 속도(대역폭)을 끌어올리는 효과도 거둘 수 있다.

이 특허는 작년 인텔이 공개한 '복수의 다이 대 다이(Die-to-Die) 상호연결 구조를 갖는 패키지 기판을 포함하는 마이크로 전자 어셈블리'의 후속적 성격을 가지고 있다. 기존 특허가 ZAM의 구조적 뼈대를 제안한 것이라면, 이번은 이를 운용할 수 있는 방법을 제시했다. 인텔은 '후면 상호 연결을 위한 자기 정렬 비아 패턴 형성'이라는 ZAM 공정 기술 특허도 확보했다.

일련의 특허는 인텔이 ZAM 기술 권리를 선점, 진입 장벽을 높이려는 시도로 풀이된다. 경쟁자가 유사한 구조로 차세대 메모리를 개발하더라도 인텔 특허를 우회할 방법을 모색해야한다는 의미다.

인텔은 일본 소프트뱅크와 협력, 소프트뱅크 자회사 사이메모리와 함께 ZAM를 개발하고 있다. 기존 HBM과 견줘 전력 소비를 40~50% 줄이는 것이 목표다. Z-앵글 구조로 제조 공정을 단순화해 생산성을 높이고, ZAM 칩 당 용량도 키울 계획이다. 인텔은 ZAM 구현을 위한 새로운 반도체 패키징 기술 'NGDB'도 함께 개발 중이다.

상용화 목표는 2029~2030년이다. 인텔은 이달 일본에서 열린 '인텔 커넥션 재팬 2026' 행사에서 ZAM 프로토타입을 처음으로 공개한 바 있다.

업계 관계자는 “HBM의 가장 큰 기술 허들은 발열과 전력 소모”라며 “인텔이 ZAM을 통해 D램 적층 구조 뿐만 아니라 AI 반도체 안에서의 배치 등 전반적인 혁신을 추진하고 있어 HBM 판도를 흔들지 주목된다”고 밝혔다.

권동준 기자 djkwon@etnews.com