삼성전자가 3나노미터(㎚) 반도체 개발에 인공지능(AI) 설계 기술을 적용했다. 반도체 칩 성능을 높이고, 개발 기간을 단축하기 위해서다. AI 기술이 첨단 반도체 설계까지 침투하고 있다.

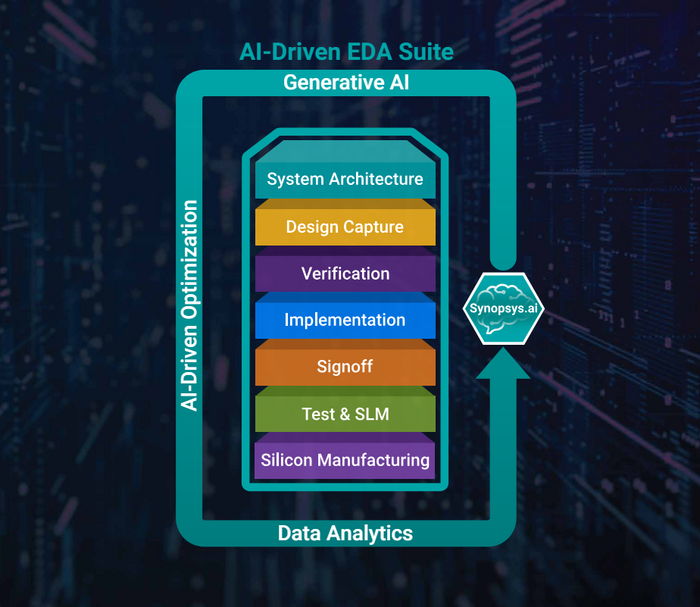

7일 업계에 따르면 삼성전자는 최근 AI 기반 반도체 설계자동화(EDA) 솔루션을 활용해 3㎚ 모바일 시스템온칩(SoC) 설계를 완료하고, 파운드리 공정 전환(테이프아웃)을 시작했다. AI EDA 솔루션은 업계 1위 시높시스와 협력했다.

삼성전자가 3㎚ 모바일 칩을 AI로 설계한 것은 이번이 처음이다. 삼성 3㎚는 차세대 트랜지스터 구조인 '게이트올어라운드(GAA)'를 적용한 첫 공정이다. 트랜지스터 핵심 구성요소인 게이트와 채널 접합면을 확대, 기존 핀펫 대비 성능을 끌어올린 것이 특징이다. 초미세 회로를 구현해야하는 만큼 설계부터 공정까지 기술 난도가 매우 높다.

이 때문에 3㎚ GAA 공정으로 칩을 설계·개발하려면 막대한 인력이 투입돼야 했다. 통상 5㎚를 기준으로 반도체를 설계하려면 100여명 이상 인력이 필요한 데, 3㎚는 이보다 많은 설계 엔지니어를 투입해야한다. 또 고객이 요구하는 반도체 성능·전력효율·크기(PPA)를 맞추는 것이 쉽지 않다.

삼성전자는 이같은 설계 어려움을 AI로 해결한 것으로 알려졌다. AI 설계는 사람이 직접 수행 시 막대한 시간과 노력이 들어가는 작업을 신속하게 해결할 수 있다. 수작업으로는 수주에서 수개월 소요되는 회로 설계를 AI EDA로 몇 시간만에 구현할 수 있다는 평가다.

삼성전자는 이번 설계 과정에서 기간을 몇 주 가량 단축한 것으로 알려졌다. 전력 효율성도 기존 대비 10% 높였다. 반도체 경쟁력을 좌우하는 PPA를 개선한 성과다. AI로 최적의 회로 설계 방법을 찾은 것이 주효했다는 후문이다.

삼성과 시높시스 협력은 AI로 첨단 반도체 역량을 끌어올린 사례로 주목된다. 초미세 공정 개발 어려움과 인력 확보 한계를 극복했기 때문이다. 반도체 설계 분야에 AI가 빠르게 침투할 단초가 될 것으로 관측된다.

AI 기반 반도체 설계 사례는 급증하고 있다. 지난해 초 시높시스가 AI 설계를 지원, 반도체 테이프 아웃을 한 사례는 100여건 수준이었지만, 하반기에는 300여건에 달한 것으로 파악됐다. 시높시스는 곧 1000건 이상 AI 적용 사례를 확보할 것으로 기대하고 있다. 또 다른 EDA 솔루션 기업인 케이던스도 AI 기반 설계 툴을 신성장 동력으로 삼고, 시장 공략을 강화하고 있다.

EDA 업계 관계자는 “반도체 회로가 미세화할수록 설계가 복잡해지고 설계 인력이 담당해야할 영역도 대폭 늘어날 수 밖에 없다”며 “설계 인력이 부족해 반도체 칩을 시장에 적시 공급하기 어려울 수 있기 때문에, 이를 AI 설계로 해결하려는 움직임이 확대되고 있다”고 전했다.

권동준 기자 djkwon@etnews.com