개발 마치고 연내 성능테스트 완료

D램 쌓아 데이터 속도 획기적 개선

AI·5G·클라우드 등 HPC 필수재

2~3년 내 12개 집적 패키징 계획

성능 향상·비용 절감 칩렛 고도화

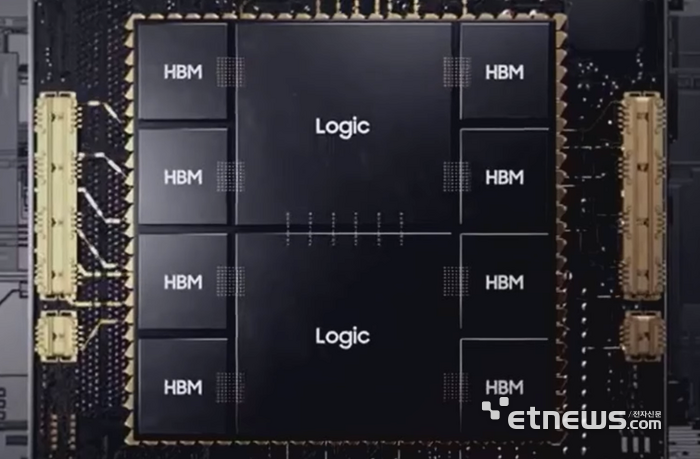

삼성전자가 고대역폭메모리(HBM)를 8개까지 탑재하는 패키징 ‘아이큐브8’ 개발을 완료하고 내년부터 양산에 돌입한다.

김종국 삼성전자 그룹장은 8일 열린 반도체 기술 워크숍에서 “앞으로 얼마나 많은 로직과 메모리를 한 패키지 안에 집적할 수 있는지가 반도체 기술 경쟁력이 될 것”이라며 이같이 밝혔다. 삼성전자는 연내 HBM 8개를 탑재한 패키징 기본 기술에 대한 성능 테스트를 완료한다는 계획이다.

HBM은 D램을 쌓아 데이터 처리 속도를 획기적으로 개선한 메모리다. 메모리 적층 난도가 높아 차세대 패키징 기술로 꼽힌다. 인공지능(AI), 5G, 클라우드, 데이터센터 애플리케이션 등으로 대표되는 고성능컴퓨팅(HPC)의 필수재로 분류된다.

챗GPT로 대표되는 생성 AI와 하이퍼 스케일급 데이터센터 수요 확대로 빠른 연산속도의 대용량 메모리 수요 또한 늘어나고 있다. 삼성전자는 2021년 4개의 HBM을 하나의 패키징으로 구현한 ‘아이큐브4’를 개발·양산했다. 이번에 8개 패키징 개발 완료에 이어 HBM 12개와 16개를 탑재한 패키징 기술 개발도 추진, 첨단 패키징 시장을 선도한다는 계획이다.

김 그룹장은 “고객사는 더 많은 덴시티(저장 용량)와 밴드위스(대역폭) 확보, 성능 향상을 필요로 한다”며 “이미 일부 고객사의 경우 HBM 12개·16개가 집적된 패키징 개발을 요구, 12개는 2~3년 내 양산을 목표로 하고 있다”고 말했다.

HBM 탑재 확대에 따라 패키지와 인터포저 영역도 약 두 배 늘어났다. 아이큐브4가 패키지 4225㎟, 인터포저 1500㎟라면 아이큐브8은 패키지 7225㎟, 인터포저 2800㎟다. HBM 12개를 탑재한 아이큐브12는 패키지 7225㎟, 인터포저 3200㎟ 이상을 갖출 것으로 예상됐다.

단일 칩의 성능 한계와 높은 비용 극복을 위해 칩 여러 개를 하나로 연결한 ‘칩렛’ 수요 확대를 고려한 결정이다. 2.5D 패키징 공정에서 반도체 인쇄회로기판(PCB)과 칩을 연결하는 인터포저 역할이 중요하다.

삼성전자는 칩을 수직으로 적층하는 3D 패키징 ‘엑스큐브’ 개발과 고도화도 병행하고 있다. 2020년 첫 선을 보인 엑스큐브 기술 1세대는 이미 HBM에 적용했으며 2세대 기술도 지난해 신뢰성 검증을 완료하고 양산을 준비 중이다.

김 그룹장은 패키징 반도체 수율이 통상 95% 수준인 상황에서 어느 회사도 달성하지 못한 수율 99.9% 달성을 목표로 제시하며 오픈 생태계를 함께 만들어가자고 제안했다. PCB, 디자인, 학계, 반도체 후공정(OSAT) 기업 등과 협업을 추진할 계획이다.

삼성전자는 칩렛이 차세대 반도체 시장에서 경쟁력을 좌우할 것으로 예상되는 만큼 패키징뿐만 아니라 최적화된 구조, 설계, 공정 기술 간 조화를 통해 칩렛 기술 고도화를 지속한다는 방침이다.

이경민 삼성전자 시스템LSI사업부 수석은 “보통 칩렛을 패키지 기술로 생각하지만 구조, 설계, 공정 분야에서 체계 기술이 준비돼야 하나의 칩처럼 동작할 수 있는 구성이 가능해진다”며 “삼성전자는 칩렛 요소 기술을 확보하고 고도화해 초미세공정 기술·비용 한계를 극복, 칩렛 성능 우위를 확보하고 파워 효율을 향상할 것”이라고 밝혔다.

성남(경기)=

박종진 기자 truth@etnews.com