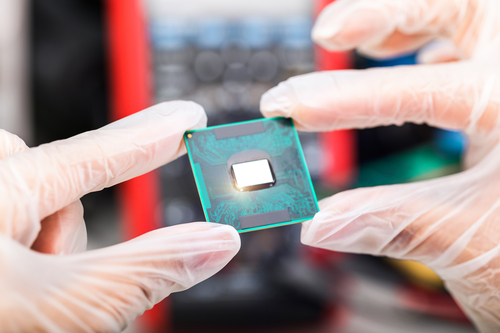

반도체 설계 전공 학부생·대학원생이 직접 설계한 반도체 칩이 공공 반도체 팹을 통해 실제로 제작, 설계검증을 할 수 있는 기회가 제공된다.

과학기술정보통신부는 1일 한국전자통신연구원(ETRI)에서 차별화된 반도체 설계 인재 양성을 위한 설계검증 서비스 착수를 위한 협약식 및 현판식을 개최했다.

이번 서비스를 통해 반도체 설계 전공 학부생·대학원생이 설계한 반도체 칩 제작을 신청하면 ETRI·서울대·대구경북과학기술원(DGIST)이 운영하는 반도체 팹에서 500㎚ CMOS(상보형 금속 산화막 반도체) 기술을 이용한 반도체 칩이 제작 및 패키징된다. 이를 통해 칩이 설계한 대로 동작하는지 직접 측정 및 분석을 통해 검증할 수 있다.

그동안은 석·박사 과정 대학원생도 주로 상용 파운드리에서 칩 제작을 의뢰해야 했으나 비싼 가격과 오랜 대기시간, 부족한 피드백 등 한계가 존재했다.

또 전문 파운드리에서 제공하는 설계지원키트(PDK)는 비밀 유지계약 하에 제공되기 때문에 학부생에게 제공되기 어렵고 수업에서도 사용되기 어려웠던 탓에 실질적인 칩 제작 기회는 사실상 없었다.

이를 해결하기 위해 국내에서 최초로 시도하는 칩 제작 서비스는 국내 공공 팹을 활용해 학부생·대학원생에게 무료로 신속하게 칩을 제작해주고, 관련 사항을 빠르게 피드백할 수 있는 체계로 추진된다.

과기정통부는 본 사업이 실전 역량을 갖춘 설계 인재를 양성하는 매우 실효적인 교육 모델이 될 것으로 기대하고 있다.

이번 서비스는 지난달 사업 참여기관이 확정된 상태로 서비스 준비를 거쳐 올해 4분기에 시범 서비스를 1회 제공할 예정이다.

이후 내년부터 2027년까지 매년 6~12회 이상 설계검증 서비스를 제공하는 것을 목표로 한다. 이를 토대로 앞으로 매년 500~1000명 이상 설계 전공 학생이 칩 제작 혜택을 받을 수 있을 것으로 예측된다.

이종호 과기정통부 장관은 “반도체 기술 패권 경쟁이 치열한 상황에서 반도체 인재 양성은 매우 중요하다”며 “보다 효율적으로 시스템 반도체 경쟁력을 확보하기 위해선 경쟁국과 차별화된 방안을 적극적으로 도입해야 하며 이번 사업을 통해 뛰어난 인재가 양성될 수 있도록 최선을 다하겠다”고 말했다.

이인희 기자 leeih@etnews.com