삼성전자가 지난해 3월 세계 최초로 양산 성공한 20나노 D램 설계, 공정 기술 핵심을 공개했다. 양산 개시 이후 1년 9개월 시간이 흘렀으나 경쟁사는 아직 20나노 D램 본격 양산을 시작하지 못하고 있다. 이 때문에 삼성전자 발표에 업계 관계자, 전문가 관심이 집중됐다.

삼성전자는 7일(현지시각)부터 9일까지 미국 워싱턴 D.C에서 열린 국제전자소자회의(IEDM:International Electron Device Meeting) 2015에서 20나노 D램 핵심 기술을 공개했다. 소자 분야를 다루는 IEDM은 국제반도체회로설계학회(ISSCC) 등과 함께 세계 3대 권위 반도체학회로 인정받고 있다. 삼성전자가 공개한 관련 논문(논문번호 26.5, 20nm DRAM:A New Beginning of Another Revolution)은 IEDM 2015 톱픽으로 선정됐다.

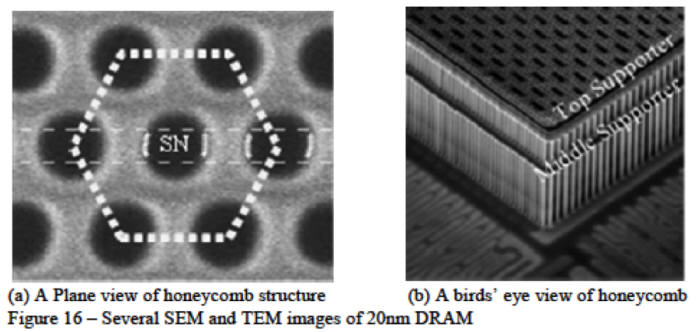

핵심은 크게 두 가지다. 우선 메모리 최소 단위인 셀 배치를 사각에서 벌집(Honeycomb) 구조로 변경했다. 셀간 거리(pitch)를 7.5% 늘리고 셀 캐패시턴스(Capacitance:전하 축적 능력을 나타내는 물리량)를 57%나 확대시켰다. 반면에 데이터를 읽고 쓸 때 활용되는 비트라인(B/L)에는 에어갭(Air Spacer)을 배치, 캐패시턴스를 34%나 감소시켰다.

박제민 삼성전자 디바이스솔루션(DS) 부문 반도체연구소 설계 수석 등 연구진은 “해당 기술은 20나노 이하 노드 D램 양산 시에도 핵심으로 활용될 것”이라고 말했다.

D램은 메모리 셀에 배치된 캐패시터에 전하를 저장한다. 저장된 전하량으로 0과 1을 판단한다. 공정 미세화가 이뤄지면 셀 면적이 좁아지는데, 이 때문에 캐패시터 용량을 사수하는 것이 점점 어려워진다. 바닥 면적이 좁아지면 원통형 커패시터 수직 길이를 늘려야 한다. 그러나 바닥 면적 대비 수직 길이비가 높아지면 커패시터가 무너져 내린다.

이중호 용인대학교 컴퓨터과학과 교수는 “셀 캐패시턴스를 57%나 확대한 것은 놀라운 성과”라며 “물리적 한계를 구조적 혁신으로 풀어냈다”고 평가했다.

비트라인 캐패시턴스를 낮춘 이유는 커플링 노이즈를 감소시키기 위한 조치다. 공정 미세화로 비트라인간 간격이 좁아질수록 노이즈는 커진다. 이는 에러율 증가, 동작속도 감소로 이어진다. 노이즈를 줄이는 방법은 비트라인의 캐패시턴스를 낮추는 것이다. 삼성전자는 이를 에어갭으로 해결했다. 에어갭을 배치하기 위해 특수 소재로 공간을 확보하고 이것을 다시 깎고(식각), 덮는(증착) 등 세 가지 생산 공정을 추가했다.

삼성전자는 20나노 D램 양산으로 경쟁사와 기술 격차를 1년 6개월 이상으로 다시 늘려놨다. 최주선 삼성전자 메모리사업부 전략마케팅팀장(부사장, 지난해까지 D램 개발팀장) 등 지난해 연말 20나노 D램 양산 성공 주역들이 대거 승진한 것도 이 같은 성과를 가볍게 여기지 않았기 때문이다.

마이크 하워드 IHS D램 부문 수석연구원은 “20나노 D램 양산 성공으로 올 한해 삼성전자 시장 점유율이 최대 전성기 시절과 동등 수준까지 올라왔다”며 “경쟁사는 점유율을 더 잃기 전에 20나노 D램 양산화를 성공시켜야 한다”고 강조했다.

한주엽기자 powerusr@etnews.com