화백엔지니어링이 전자회로기판(PCB) 습식 에칭(식각) 공정용 ‘에칭팩터(etching factor) 개선제’를 개발, 기판 미세회로를 형성하고 공정 비용을 절감할 수 있는 길을 열었다.

기존 도금 공정 대비 30% 이상 공정비용을 줄일 수 있고 최근 샘플링이 이뤄지고 있는 30, 40피치(pitch) 반도체 패키지 기판까지 가능하다.

화백엔지니어링(대표 이강)은 최근 PCB 회로 형성공정에서 회로 측면부 에칭을 효과적으로 억제하는 에칭팩터 개선제를 개발, 일부 고객사에 공급하기 시작했다.

에칭공정은 에칭액 등 화학약품으로 원하는 회로 형상만 남기고 부식시키는 습식 에칭과 플라즈마 챔버에 에칭가스를 주입해 부식을 일으키는 건식 에칭으로 나뉜다.

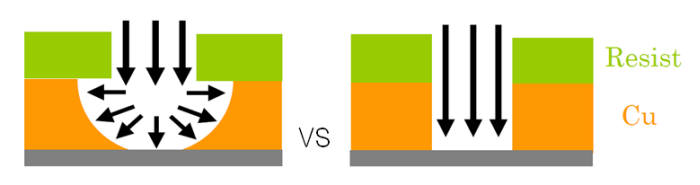

반도체 공정에 주로 쓰이는 건식 에칭과 달리 습식 에칭은 상대적으로 저렴해 PCB 공정에 사용되지만 약품이 직접 표면에 닿는 공정 특성상 수직뿐만 아니라 모든 방향으로 부식이 진행되는 등방성이 단점이다. 가로 방향으로도 부식이 일어나기 때문에 회로 선폭과 선 간 공간을 미세하게 형성하는 데 한계가 있다.

최근 휴대폰 주기판(HDI) 회로 밀도 증가로 제조사는 선폭과 선 간 공간을 합쳐 80피치급 기판을 요구하지만 습식 에칭으로는 한계가 있다. 반도체 패키지 기판 역시 기존 60~70피치 제품은 습식 에칭으로 가능하지만 60피치 이하 50피치 제품은 추가 후가공 비용이 발생하는 MSAP 도금 공정을 거쳐야 한다.

화백엔지니어링이 개발한 에칭팩터 개선제는 약품을 투입하는 스프레이 압력차를 이용, 회로 측면에 결합해 수평 방향 부식을 억제한다. 부식 억제 성분을 에칭액 중에 균일한 농도로 용해·분산시키는 기술이 핵심이다. 에칭 머신에 적용할 수 있는 약품 샘플링·센싱 박스와 에칭 컨트롤러 기술을 함께 보유해 일정한 농도를 유지할 수 있다.

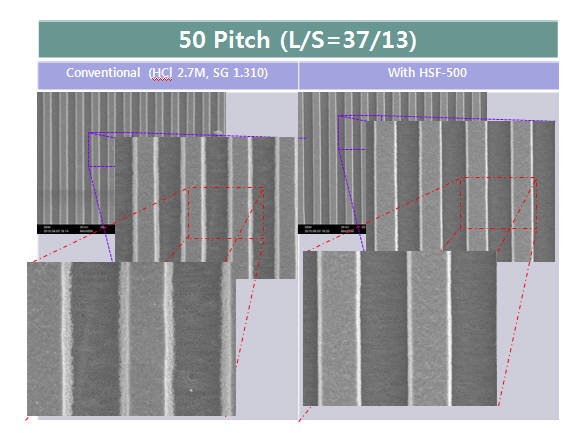

50피치 반도체 패키기 기판 기준으로 기존 방식은 에칭팩터가 4가 나오는 반면에 화백엔지니어링 개선제를 활용하면 9~10까지 에칭팩터를 확보할 수 있다. 에칭팩터는 가로 방향 부식 각도를 수치화한 것으로 숫자가 클수록 수직에 가깝다는 것을 의미한다. 추가 도금 없이 회로 단면적을 2마이크로미터(㎛) 높게 형성할 수 있고 회로 바깥 쪽 표면이 깔끔해 전기저항과 임피던스 등 기판 성능 향상에 유리하다.

업계는 도금 방식으로 제조하는 패키지 기판을 에칭 방식으로 전환하면 30% 이상 공정 비용 절감이 가능할 것으로 보고 있다. 향후 30피치 패키지 기판까지 대응 가능해 대만, 중국 등 해외 PCB업체에 비해 원가·제품 경쟁력이 높아질 전망이다.

이강 화백엔지니어링 대표는 “기존 제품을 개선한 수준이 아닌 새로운 개념의 제품을 고객사 요구에 맞춰 개발한 것”이라며 “일본 케미컬 회사 등으로부터 국내 시장을 지키고 우리 PCB업계 산업 경쟁력 강화에 일조할 것”이라고 말했다.

박정은기자 jepark@etnews.com