스마트폰용 애플리케이션프로세서(AP) 등 비메모리 반도체에 14나노미터 핀펫 공정을 적용·양산한 데 이어 메모리 반도체도 10나노급 시대를 앞뒀다. 삼성전자와 SK하이닉스 등 세계 반도체 시장을 주도하는 제조사들이 28나노 D램에 이어 20나노 초반대 D램 양산 비중을 올해 확대한다. 10나노급 D램 양산 기술 개발에도 속도를 내고 있다.

낸드플래시나 비메모리에 비해 상대적으로 기술 난이도가 높은 D램 분야에서 10나노대를 실현하려면 많은 변화가 필요하다. 선폭을 줄이기 위해 반도체 설계·공정·재료는 물론이고 후공정 분야까지 전반적인 기술 진화가 요구된다.

반도체 업계에서는 10나노급과 10나노 이하 반도체를 실현하는 기술에 대해 여러 가능성을 타진하고 있다.

과거 60나노급 칩과 40나노급 칩을 생산할 때도 미세공정 전환의 한계는 늘 지적돼왔다. 20나노대 반도체는 불가능할 것이란 시각도 제기됐었다. 하지만 기업들은 현재 최첨단 기술의 20나노대 반도체를 비용 효율적으로 양산하고 있다.

10나노급과 10나노 이하 미세공정은 높은 기술 난이도를 뛰어넘는 것뿐만 아니라 가장 비용 효율적인 방법을 구현해야 하는 두 마리 토끼를 모두 잡아야 가능하다.

예를 들어 기술적으로 5나노 칩을 생산하는 기술을 갖추더라도 20나노 칩을 생산하는 것보다 비용과 시간이 몇 배 더 들면 생산성이 떨어지기 때문이다. 칩을 구매하는 기업 역시 제품이 주는 효율보다 더 많은 비용을 지불해야 하므로 결국 시장성이 떨어질 수밖에 없다.

◇멀티패터닝 vs EUV

현재 EUV 노광장비 선도 기술을 보유한 회사는 네덜란드 ASML뿐이다. 일본 니콘도 EUV 기술과 장비를 보유했지만 정밀도 면에서 ASML과 격차가 큰 것으로 시장은 평가한다.

10나노급 EUV 장비를 위한 기술 개발이 늦어지고 천문학적 비용이 소요되면서 반도체 제조사들은 패턴을 여러 번 덧입히는 멀티 패터닝 기술을 중점적으로 개발하고 있다. 사실상 EUV 장비 개발을 ASML 혼자 주도하고 있어 마냥 기다릴 수 없기 때문이다. 인텔, 삼성전자, TSMC는 EUV 장비 개발을 위해 ASML에 지분을 투자했지만 EUV 장비 없이 미세공정을 실현하는 기술을 각각 개발하고 있다.

ASML은 멀티 패터닝보다 EUV 공정을 도입했을 때 반도체 생산까지 거치는 과정이 줄어들어 시간과 비용을 훨씬 아낄 수 있다고 분석한다. 기존 이머전 장비를 사용하면 20나노 공정에서 마스크가 23개, 7나노에서는 33개가 필요하다. 20나노에서 7나노로 미세화하면 공정 과정이 4배 이상 늘어나 정확도가 떨어질 수 있고 비용 증가도 감수해야 한다.

하지만 EUV 장비를 사용하면 7나노에서 마스크 수를 9개로 줄일 수 있다고 ASML은 분석했다. EUV 장비를 쓰면 10나노에서도 기존 20나노 수준의 공정으로 충분해 경제성에서 앞선다는 설명이다.

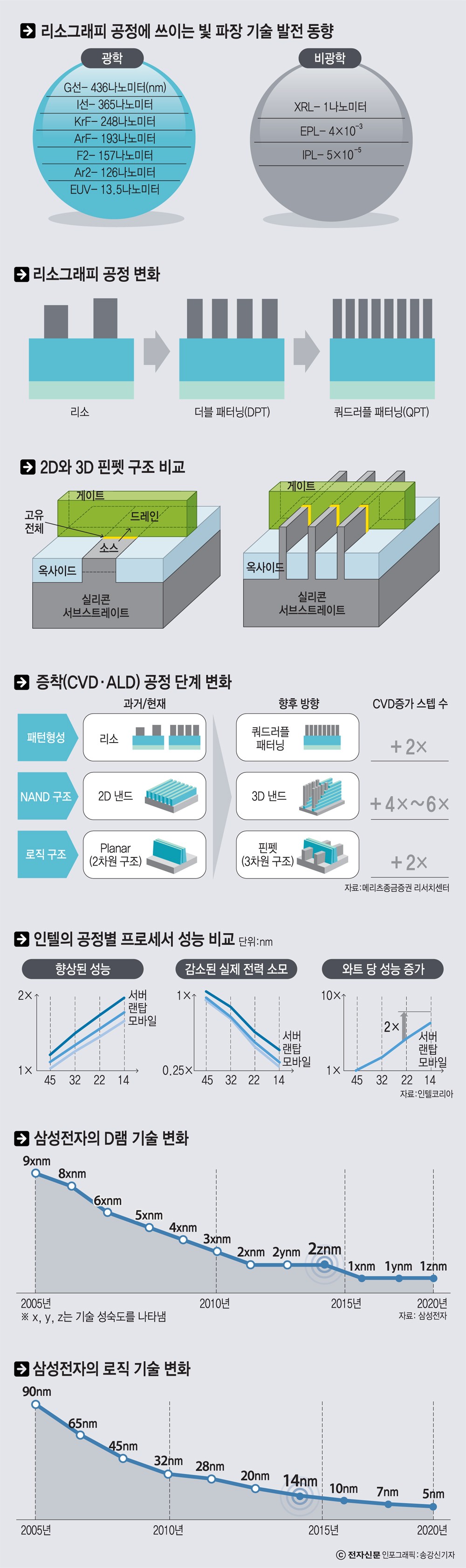

EUV는 노광 장비에서 광학을 이용한 가장 마지막 단계의 기술로 꼽힌다. 노광 장비는 나노미터급인 빛의 단파장 길이에 따라 G선, I선, 불화크립톤(KrF), 불화아르곤(ArF), F2 레이저, Ar2 레이저, 극자외선(EUV) 순으로 발전해왔다.

파장이 13.5나노미터에 불과한 EUV 이후는 광학 대신 방사선을 사용할 것으로 전문가들은 내다본다. 파장이 1나노미터인 XRL(엑스레이 리소그래피), 1나노 이하 수준인 전자빔투사(EPL), 이머전포토리소그래피(IPL)가 차세대 노광 기술이 될 것으로 거론된다.

하지만 EUV 기술 개발이 더뎌지면서 공정 미세화를 위해 ArF에서 ArF 이머전으로 발전한 데 이어 더블 패터닝, 쿼드러플 패터닝 등으로 새롭게 기술이 진화하고 있다.

◇높이 쌓는 3차원 반도체

기존 포토 공정을 그대로 사용하면서 전력 소모를 줄이고 데이터 처리 용량을 늘릴 수 있도록 반도체 구조를 3차원으로 변화시키는 기술도 진화하고 있다. 고성능 D램은 3차원 칩이 일정 성능 면에서 멀티 패터닝의 한계를 넘어서는 것으로 평가받는다. 인텔과 삼성전자가 양산 중인 14나노 핀펫(FinFET)이 대표적이다.

수직으로 칩을 쌓아올려 수직으로 관통하는 구멍을 낸 뒤 연결해 전기적 신호 효율성을 높이는 패키징 기술인 ‘실리콘관통전극(TSV)’이 D램과 낸드플래시에 적용됐다. 회로 선폭을 줄이지 않고도 반도체 패키지 크기와 전력 소비를 획기적으로 줄이면서도 용량은 늘릴 수 있다. 서로 다른 반도체를 하나의 칩으로 연결할 수 있는 기술이다.

낸드플래시는 게이트에 전하를 저장하는 방식의 플로팅 게이트 구조였으나 공정 미세화로 한계에 달했다. 단층으로 배열한 셀을 수직으로 쌓는 3차원 방식으로 새로운 돌파구를 찾았다. 최소 20단에서 최대 70단까지 쌓는 기술이 개발됐다.

3차원 반도체는 기존 평면형 구조와 달리 수직으로 게이트를 쌓기 때문에 반도체 공정 중 증착 공정을 반복해야 하므로 생산 비용과 시간이 증가한다. 업계에서는 3D 낸드에서 증착 공정이 4~6배 늘어난 것으로 분석한다.

미세공정 기술 개발 속도가 더딘 상황에서 3차원 반도체는 테라바이트(TB) 수준의 메모리를 개발할 수 있는 기반이 될 전망이다.

TSV는 향후 무선 혹은 광학 기술을 적용해 칩 간 연결을 실현하게끔 진화할 것으로 예측된다. 적층 단수를 높이고 칩간 연결 속도를 개선하는 연구를 업계에서 진행 중이다.

인텔은 2016년에 10나노 칩을 선보인다는 목표다. 내부적으로 10나노 이하 기술 개발 로드맵을 수립하고 연구를 진행 중이다. 삼성전자도 오는 2020년 전까지 5나노미터급 모바일 AP를 개발하겠다는 전략이다.

배옥진기자 withok@etnews.com