KAIST 경종민 교수팀

우리나라는 세계 최대 규모의 반도체 생산 대국이다. 반도체산업은 90년대 우리 경제의 화두라 할 만큼 국가 경제에 지대한 공헌을 해왔다.

단군이래 최대의 경제위기라 하는 IMF 구제금융시대에도 반도체는 자신의 역할을 충실하게 수행, 경제위기를 벗어나게 한 효자산업이다.

반도체의 역할은 여기서 그치지 않는다. 자신 스스로 국내 수출의 최고봉에 올라 있으면서 전자·정보통신산업을 OECD국가 중 4위로 끌어올리는 견인차 역할을 담당했다.

이러한 반도체산업 발전의 핵심에 KAIST 전기 및 전자공학과 경종민 교수팀이 있다. 경 교수는 그간 반도체설계교육센터를 이끌면서 국내 반도체 인력양성에 지대한 공헌을 해왔다. 또 KAIST 연구원들과 함께 미래 반도체산업을 주도할 새로운 신기술 개발에 박차를 가하고 있다.

연구팀의 주요 연구과제는 반도체 설계 지원 기술과 차세대 고성능 칩 개발을 위한 C/HDL 혼합설계검증엔진(iSAVE:InSystem Algorithm Verification Engine), DIVA(DualIssue VLIW Architecture) 등이다.

C/HDL 혼합설계검증엔진은 복잡한 칩 설계시 에뮬레이션을 통해 작동 여부를 검증하는 데 필요한 기반 기술이다.

이 엔진이 개발되면 칩 설계에 필요한 전체 시간을 줄여 신제품 개발에 따른 비용과 기간을 획기적으로 절감할 수 있다. 특히 기존 설계 검증 에뮬레이션이 칩 설계 마지막 단계에 이뤄지는 데 비해 초기단계에서 칩의 정확한 동작을 검증할 수 있어 관련분야에 큰 도움이 될 전망이다.

VDSM(Very DeepSubMicron) Datapath 합성기 개발도 연구팀이 추진하는 주요 연구사업 중 하나다.

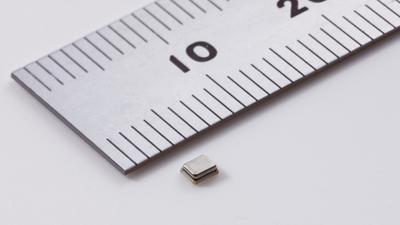

최근들어 반도체 제조공정의 선폭은 크게 줄어들고 있다. 또 소자들이 소형화되고 속도가 빨라짐에 따라 소자 자체의 성능보다는 연결선로의 시간지연 영향이 커지고 있다.

기존 반도체 설계에서 칩의 배치와 연결은 자동화된 툴을 이용해 왔다. 또 고성능 칩을 설계하기 위해 전 공정을 디자이너가 직접 설계하는 등 불편함이 적지 않았다. 이러한 기존 방식은 설계의 품질은 높지만 디자인 사이즈가 증가함에 따라 설계 시간과 비용면에서 많은 부담을 안고 있다.

연구팀은 소자 소형화에 따른 속도 향상을 전체 성능으로 연결시키기 위해 소자 중심의 설계방식에서 벗어나 배치와 연결 중심의 설계가 이루어져야 한다고 판단하고 있다. VDSM Datapath 합성기 개발은 바로 이런 맥락에서 진행된다.

이에 따라 연구팀은 배치와 연결을 자동화하는 툴, VDSM Datapath 합성기를 개발하고 있다.

이 방법은 기존 방법과는 달리 완전히 자동화된 레이아웃 생성을 지향하는 것이 아니라 설계에 따른 여러 기술을 툴에 반영해 설계자가 전체 공정 수준의 레이아웃을 자동으로 만들어낼 수 있다.

뿐만 아니라 전자·정보통신산업의 발달에 따라 특정 응용영역의 알고리듬을 효과적으로 구현할 수 있도록 하는 MetaCore 개발도 추진하고 있다.

이밖에 고성능 마이크로프로세서 설계도 중점 연구사업이다.

최근 5년간 연구팀은 20여개의 수탁 연구과제를 수행해 386, 486 칩세트를 독자적으로 개발했다. 또 차세대 MPU기술 개발 프로젝트를 통해 펜티엄 호환칩 개발에 성공함으로써 우리나라의 비메모리 설계기술을 선진국 수준으로 끌어올렸다.

연구팀은 이 기술을 토대로 Flex 고속 페이저 개발 및 퍼스널 컴퓨터의 온칩화 프로젝트를 이끄는 등 개인정보단말기(PDA) 및 휴대형 이동통신단말기 등을 위한 프로세서 코어의 저전력화 연구사업을 진행하고 있다.

대전=김상룡기자 srkim@etnews.co.kr

경제 많이 본 뉴스

-

1

5년 전 업비트서 580억 암호화폐 탈취…경찰 “북한 해킹조직 소행”

-

2

LG이노텍, 고대호 전무 등 임원 6명 인사…“사업 경쟁력 강화”

-

3

롯데렌탈 “지분 매각 제안받았으나, 결정된 바 없다”

-

4

'아이폰 중 가장 얇은' 아이폰17 에어, 구매 시 고려해야 할 3가지 사항은?

-

5

美-中, “핵무기 사용 결정, AI 아닌 인간이 내려야”

-

6

삼성메디슨, 2년 연속 최대 매출 가시화…AI기업 도약 속도

-

7

美 한인갱단, '소녀상 모욕' 소말리 응징 예고...“미국 올 생각 접어”

-

8

아주대, GIST와 초저전압 고감도 전자피부 개발…헬스케어 혁신 기대

-

9

국내 SW산업 44조원으로 성장했지만…해외진출 기업은 3%

-

10

반도체 장비 매출 1위 두고 ASML vs 어플라이드 격돌

브랜드 뉴스룸

×

![]()