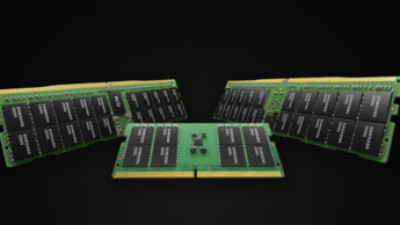

삼성전자·TSMC가 첨단 반도체 패키징 분야에서 '하이브리드 본딩'을 두고 한판승부를 펼칠 전망이다. 하이브리드 본딩은 반도체 성능을 끌어올릴 차세대 패키징 기술로 삼성전자는 메모리 분야에서, TSMC는 시스템 반도체 분야에서 연구개발(R&D) 역량을 쏟는 것으로 나타났다.

최광성 한국전자통신연구원(ETRI) 저탄소집적기술창의연구실장은 '종합반도체기업(IDM)과 반도체 위탁생산(파운드리) 기업의 첨단 패키징 기술 동향 분석' 주제 발표에서 이같이 밝혔다.

양사 최신 논문과 기술 연구 방향을 비교 분석한 결과, 삼성전자와 TSMC는 하이브리드 본딩을 반도체 패키징 핵심 기술로 낙점한 것으로 파악된다고 설명했다.

하이브리드 본딩은 기존 솔더볼이나 범프 대신 '구리와 구리' 등 저항이 적은 물질로 반도체를 직접 연결하는 방식을 의미한다. 반도체 성능과 품질을 개선할 수 있어 기술 확보 경쟁이 치열하다.

삼성전자와 TSMC는 각사의 강점을 부각하는 방향으로 기술을 고도화하고 있다. 삼성은 고대역폭메모리(HBM)를 중심으로 한 하이브리드 본딩 기술 개발에, TSMC는 시스템 반도체 강자로서 패키징 기술 고도화에 집중하고 있었다.

최 교수는 “삼성전자는 반도체 소재 및 공정 메카니즘이나 강도 측정 등 기본적인 기술 요소에 대한 R&D에 집중하고 있다”며 “TSMC는 패키징 기술을 실제 제품에 적용했을 때 어떤 결과를 도출할 수 있는지 중점 연구하는 것으로 확인됐다”고 말했다.

또 삼성전자는 패널레벨패키징(PLP) 기술 개발도 지속하고 있다고 전했다. 둥근 웨이퍼 대신 사각 패널 위에서 패키징하는 기술로, 끝단에 버리는 칩이 없어 생산성이 높다. 삼성은 PLP에 적합한 소재는 무엇이 있고 첨단 패키징 기술로 갈수록 어떤 소재를 개발해야 하는지 등을 중점 연구 중인 것으로 보인다.

TSMC는 패키징 모듈 고도화를 R&D 방향으로 설정한 것으로 파악된다. 전기적 성능을 강화하고 전력 효율을 높이는 방법을 지속적으로 찾는다는 의미다.

박종진 기자 truth@etnews.com