반도체 패키징은 전공정에서 완성된 웨이퍼 칩을 기판과 전기 신호를 주고받을 수 있도록 연결하고 외부 환경으로부터 보호하는 과정을 의미한다.

패키징은 과거 반도체 8대 공정 중 하나로만 여겨졌다. 현재는 반도체 성능을 획기적으로 향상시킬 대안으로 주목받는다. 전공정에서 회로 선폭이 줄어드는 속도가 더뎌지고 개발 비용도 천문학적으로 들기 때문이다.

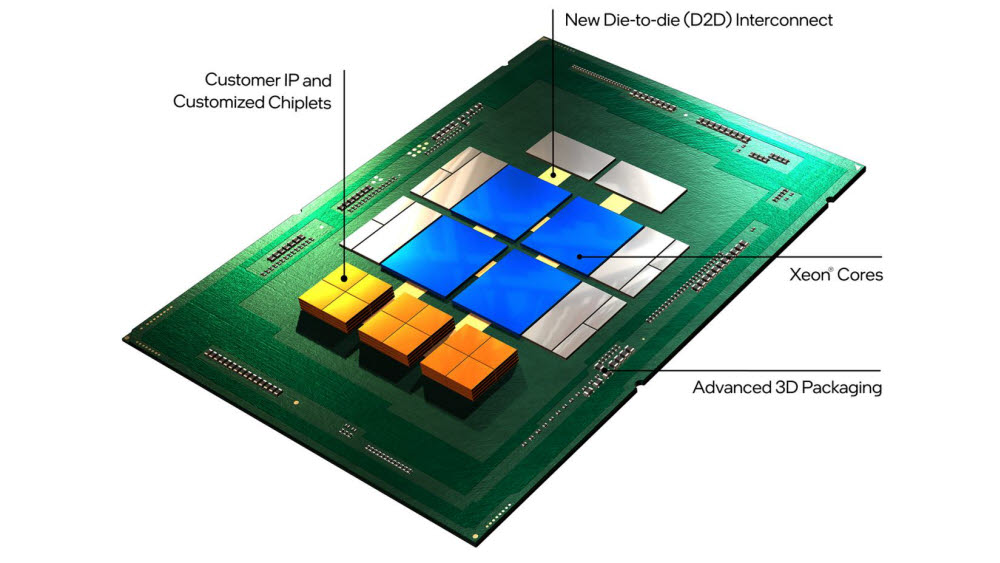

반도체 패키징은 단품 패키지를 보드에 각각 실장하던 기존 방식에서 여러 반도체 장치를 하나의 패키지 안에 통합하는 형태로 발전하고 있다. 단일 면적 내에 트랜지스터 집적도를 높이기 위해선 수직화가 필요하다.

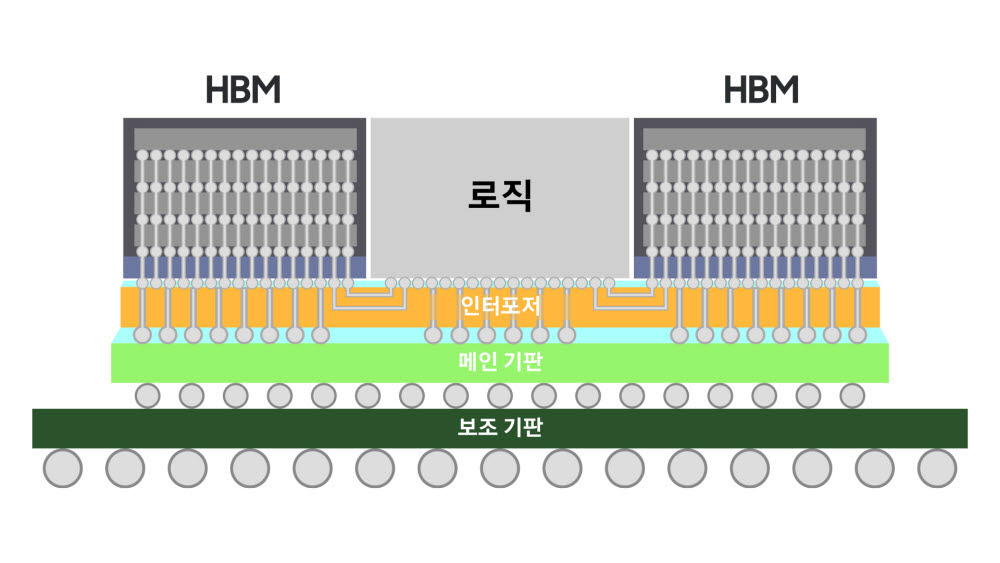

반도체업계는 2.5D 패키징 3D 패키징 등 적층 기술 개발에 힘써왔다. 2.5D 패키징은 실리콘 인터포저 위에 중앙처리장치(CPU), 그래픽처리장치(GPU) 등 로직 반도체와 고대역폭메모리(HBM)를 연결하는 방식이다. 실리콘 인터포저를 통해 집적도를 높인 후 기판과 신호를 주고받는다.

3D 패키징은 칩을 수직으로 쌓아 연결한다. 칩간 접속 거리가 가까워져 신호 지연이 감소하고 전력 소모도 줄일 수 있다. 다만 발열 역시 많아질 수 있다.

칩을 수직으로 연결하는 방식 역시 진화하고 있다. 칩에 미세한 구멍을 뚫고 전극을 형성해 관통하는 실리콘 관통 전극(TSV), 미세한 구리 볼(범프)로 연결하는 마이크로범프, 범프 대신 구리를 집어넣고 열을 가해 칩을 연결하는 하이브리드 본딩 등이 등장했다. 연결 거리를 좁혀 신호 전달 속도를 빠르게 하기 위해서다.

반도체 제조업체는 차세대 패키징 기술을 고도화하고 있다. 삼성전자는 2020년 8월 시스템온칩(SoC)과 S램을 TSV로 연결한 3D 패키징 기술 '엑스(X)-큐브'를 공개했다. 지난해 11월에는 기판 크기를 줄이면서 HBM 6개를 탑재한 2.5D 패키징 '에이치(H)-큐브'를 개발했다. 삼성전자는 2.5D와 3D 패키징을 결합한 3.5D 패키징 양산을 준비하고 있다.

TSMC는 지난해 HBM 8개를 탑재할 수 있는 5세대 CoWoS(Chip-on-Wafer-on-Substrate)를 개발했다고 밝혔다. 3D 패키징에 하이브리드 본딩을 적용하는 등 상대적으로 기술 우위에 있다는 평가를 받는다.

인텔은 로직 반도체를 서로 수직으로 연결한 3D 패키징 '포베로스' 기술을 2018년 발표했다. 이종칩을 결합한 프로세서 '메테오레이크'도 내년에 출시할 예정이다.

시장조사업체 욜디벨롭먼트는 첨단 패키징 시장이 지난해 27억4000만달러에서 2027년 78억7000만달러로 연평균 19% 성장할 것으로 전망했다. 여기에 발맞춰 글로벌 반도체 업체는 후공정 투자를 확대하고 있다.

반도체 후공정(OSAT) 산업 역시 빠르게 성장하고 있다. 그러나 글로벌 OSAT 상위 10개 기업에 국내 기업은 없는 것이 현실이다. 국내 OSAT 역시 팬아웃 패널레벨페키지(FO-PLP), 웨이퍼레벨패키지(WLP) 등 고부가 패키징 생산 확대에 나서고 있다. 해외업체와 투자 규모 차이가 크게 나는 만큼 글로벌 경쟁력 확보를 위해 국가 차원의 로드맵이 필요하다고 전문가들은 입을 모은다.

첨단 반도체 패키징 시장 규모

첨단 반도체 패키징 시설 투자 순위

자료 : 욜디벨롭먼트

![[테크코리아 미래기술 40]차세대 패키징](https://img.etnews.com/photonews/2209/1570318_20220913124823_531_T0001_550.png)

![[테크코리아 미래기술 40]차세대 패키징](https://img.etnews.com/photonews/2209/1570318_20220913124823_531_T0002_550.png)

송윤섭기자 sys@etnews.com