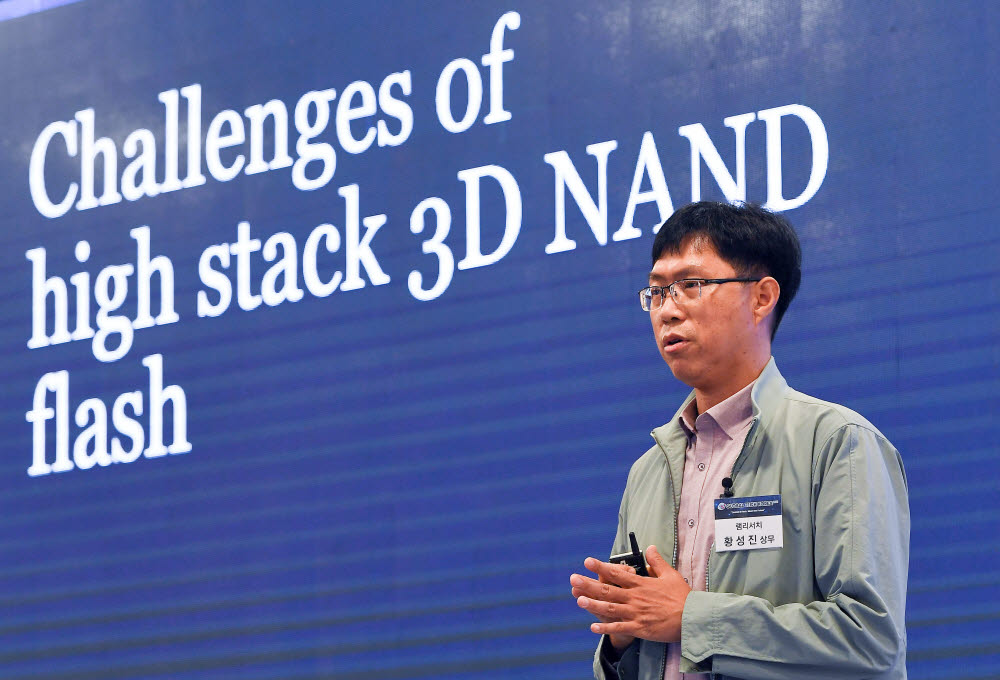

황성진 램리서치 상무는 '3D 낸드플래시 제조기술'을 주제로 낸드플래시의 스택(단수) 증가에 따른 제조 이슈와 해결 방안들을 소개했다.

데이터를 저장하는 용도의 낸드플래시는 과거에는 평면상에서 칩을 작게 구현하는 2차원 구조였다. 그러나 한정된 공간에 수많은 데이터를 담아야 해 기존 2차원 구조로는 한계가 있었다.

이에 등장한 것이 3차원 개념이다. 수직으로 쌓아 올린 공간에 구멍을 내 각 층을 연결하는 3D 낸드가 개발됐다.

24단부터 시작된 3차원 낸드는 현재 170단을 넘어 200단을 향하고 있다. 그런데 단수가 높을수록 제조 과정 중에 문제가 생긴다.

스택(실리콘 산화막·실리콘 질화막)을 쌓을수록 웨이퍼가 휘어지는 이슈(Wafer Wapage)가 발생하는 것이다.

웨이퍼가 틀어지면 제대로 스택을 쌓기 힘들고 웨이퍼를 핸들링하기 어려워지는 등 제조 공정에 문제가 생길 수 있다. 궁극적으로 낸드플래시 수율과 품질을 담보할 수 없게 된다.

예를 들어 아파트를 지을 때 고층 아파트라고 해도 건물이 휘어져 있으면 불안해지고 언제 어떤 사고가 발생할지 모르는 것과 같은 셈이다.

황 상무는 “120단까지는 웨이퍼의 뒤틀림 이슈가 크지 않았는데, 170단 이상 '하이(High) 스택'으로 3D 낸드가 진화하면서 웨이퍼가 휘어지거나 구부러지는 웨이퍼 와피지 현상이 심화하고 있다”고 설명했다.

램리서치는 이를 해결하기 위해 '벡터(VECTOR)'라는 기술을 개발해 대응하고 있다고 설명했다.

벡터 개념을 요약하면 웨이퍼 후면에도 실리콘 산화막이나 실리콘 질화막을 증착해 웨이퍼 와피지 현상을 최소화하는 것이다.

황성진 상무는 구체적인 회사와 제품에 대해서는 공개하지 않았지만 반도체 소자 업체가 벡터 기술을 이용해 3D 낸드플래시를 실제 양산하고 있다고 소개했다.

황 상무는 또 낸드플래시는 앞으로 200단 이상 지속적으로 고적층 기술 발전이 예상돼 웨이퍼 뒤틀림 이슈를 해소하고 효과적으로 대처하는 기술 개발이 뒷받침돼야 할 것이라고 강조했다.

램리서치는 ASML, 어플라이드 머티어리얼즈, 도쿄일렉트론(TEL)과 함께 세계 4대 반도체 장비사로 꼽히는 기업이다. 국내 반도체 소자 업체들과 협력을 위해 한국에 연구개발(R&D)센터를 건립하기로 했다.

윤건일기자 benyun@etnews.com