삼성전자가 차세대 엑시노스 애플리케이션프로세서(AP) 후공정 패키지 작업을 외부 업체에 맡기는 방안을 검토하고 있다. 현재로선 10나노 이하 칩 패키지 작업을 직접 수행할 능력이 부족하다고 판단했기 때문이다. 이 때문에 회사 내부에선 장기 관점으로 패키지 분야 기술 경쟁력을 높여야 한다는 목소리가 나오고 있다.

7일 업계에 따르면 삼성전자 시스템LSI사업부는 최근 국내에 대형 공장을 운용하고 있는 미국과 중국계 외주반도체패키지테스트(OSAT:Outsourced Semiconductor Assembly and Test) 업체에 7나노, 8나노 칩 패키징 개발 건을 의뢰했다.

미국 업체는 퀄컴 물량을 소화하기도 힘들다는 이유로 삼성 측 제안에 즉답을 내놓지 않은 것으로 전해졌다. 중국계 업체는 개발이 가능하다는 의사를 전달했다. 이를 확인한 삼성전자는 직접 개발(플랜A)과 외주화(플랜B)를 놓고 고심 중이다. 삼성전자는 이달이나 늦어도 다음 달까지 결정을 내려야 개발과 실제 양산을 거쳐 연말 고객사에 완성 칩을 공급할 수 있다. 삼성전자가 중국계 업체에 패키징 작업을 맡기게 되면 엑시노스 사업을 시작한 이래 처음으로 외주 제작을 의뢰하게 된다. 이 때문에 관련 업계와 기술 관계자가 삼성전자 결정에 촉각을 세우고 있다.

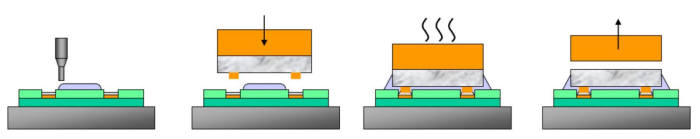

삼성전자가 외주화를 고려하게 된 배경은 경험 부재 때문이다. 웨이퍼 전공정을 마친 실리콘 칩(Die)과 패키지 기판을 접합하는 과정에서 문제가 노출됐다. 선폭이 미세화되면 칩 면적은 작아지지만 기능이 많아져 입출력(IO) 단자는 늘어난다. 단자 간 거리가 좁아진다. 일반 패키지 작업은 틴-실버(SnAg) 도금 작업을 거친 표준 지름의 솔더볼이 실리콘 칩과 패키지 기판 간 전기 접합 매개체 역할을 했다. 그러나 IO 단자 간격이 좁아진 초미세 반도체는 혹시 생길지 모를 간섭을 없애기 위해 IO 단자마다 표준 솔더볼 대비 크기가 작은 구리(Cu) 기둥(Pillar)을 세운 뒤 솔더 캡을 씌운다. 이후 칩을 기판 위에 올리고 열처리 장비에 넣으면 솔더가 녹아 기판에 붙게 된다. 이 같은 열 처리 실장 작업을 업계에선 리플로우(Reflow) 공정이라고 부른다.

10나노 이하 칩은 기존 리플로우 공정을 활용할 수 없다. 단순히 열만 활용하면 얇은 구리 기둥이 휘어지는 등의 문제가 발생하기 때문이다. 대안으로 떠오른 것이 바로 열압착(써멀콤프레션, TC) 방식의 공정이다. 칩과 기판 사이에 전기가 통하는 페이스트나 필름을 넣고 열과 압력으로 접합 작업을 수행한다. OSAT는 이 공정 기술에 대한 경험을 보유하고 있다. 삼성전자는 양산 경험이 없는데다 이 공정을 수행하려면 장비 투자도 새롭게 해야 한다. 그러나 현재로선 시간이 촉박하기 때문에 외주 카드를 만지작거리고 있는 것이다.

업계 관계자는 “퀄컴은 이미 과거부터 TC 방식으로 패키징 작업을 수행해왔다”면서 “그간 삼성전자 내에서 패키징 분야의 중요성이 크게 부각되지 않았는데, 이번 건을 계기로 사내 분위기가 바뀔 지 주목된다”고 말했다. 외주 작업을 맡기면 물류비와 작업비 등이 추가돼 원가 측면에서 불리하기 때문이다.

한주엽 반도체 전문기자 powerusr@etnews.com