인텔, 공정 전환 주기 3년으로…파운드리 업체도 늦출 듯

2년마다 트랜지스터 집적도가 두 배 증가한다는 인텔 창업자 고든 무어의 이론이 깨졌다. 인텔이 2년에 한 번 행하던 공정 전환 주기를 3년으로 바꾼다고 공식 발표했다. 삼성전자와 TSMC 등 파운드리 업체도 파생 공정을 연이어 개발하며 공정 전환 주기를 늦출 것으로 전망된다. `무어의 법칙`이 역사 속으로 사라지고 있다.

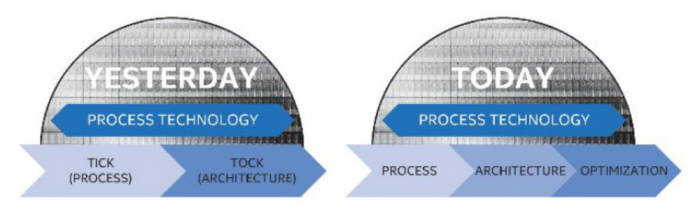

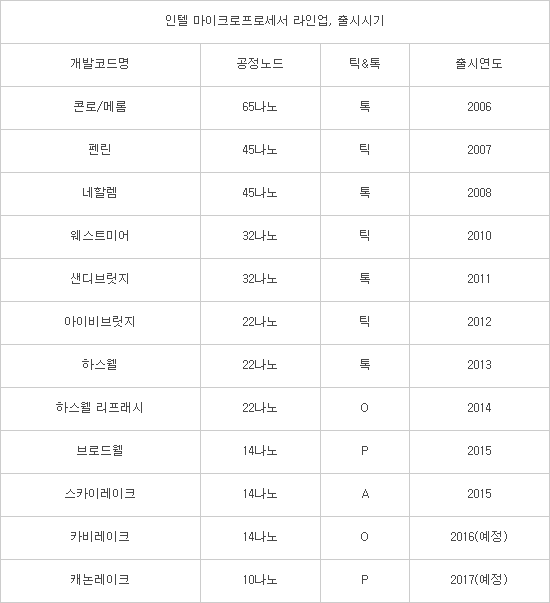

11일 업계에 따르면 인텔은 2년에 한 번 물리적 회로 선폭을 좁히는 `틱-톡` 주기를 3년으로 변경했다. 틱은 물리적 공정 전환, 톡은 아키텍처 변경을 각각 의미한다. 최근 인텔은 PAO(Process-Architecture-Optimization) 모델을 제시했다. 프로세스(P)는 물리적 공정 전환, 아키텍처(A)는 논리적 회로 구조, 최적화(O)는 논리적 회로 구조를 각각 일부 개선한다는 의미다. 2년마다 물리적 공정을 좀 더 미세화하는 주기는 이제 3년으로 변경된 셈이다. 인텔은 최근 미국 증권거래위원회(SEC)에 제출한 사업 보고서에서 이 같은 프로세서 공정 로드맵을 조용히 밝혔다.

업계 관계자는 “기술 진보를 뜻하는 인텔의 `틱톡 시계`는 그동안 한 치의 오차도 없이 쉬지 않고 돌아갔지만 22나노 공정을 14나노로 전환할 때 이 같은 3년 모델이 처음 도입됐다”면서 “이제 14나노, 10나노에서도 3년 주기로 공정이 전환될 것을 인텔이 공식 인정한 것”이라고 설명했다.

인텔이 이처럼 공정 전환 주기를 늦춘 이유는 원가가 높아지기 때문이다. 집적도나 성능만 따지면 무어의 이론은 여전히 유효하다. 그러나 3D 핀펫 구조 도입, 노광 장비 성능 한계에 따른 멀티 패터닝 적용 등으로 웨이퍼 1장으로 뽑아낼 수 있는 칩 수가 늘어도 원가가 높아지는 것이 문제다. 원가 절감을 할 수 없다면 무어의 이론을 지속시킬 이유가 없는 것이다.

삼성전자와 TSMC 같은 파운드리 업체도 10나노대 공정을 도입하면서 파생 공정을 늘리고 있다. 원가 경쟁력을 높이기 위한 조치다. TSMC는 2014년 말 첫 번째 16나노 핀펫(FF) 공정을 발표했다. 2015년 초에는 16나노 핀펫 플러스(FF+:FinFET Plus) 공정을 개발했다. 최근에는 16나노 FF+보다 성능을 더 개선한 핀펫 콤팩트(FFC:FinFET Compact) 공정 칩 양산에 들어갔다. 삼성전자도 1세대 14나노 공정인 LPE(Low Power Early)와 이보다 소비전력을 15% 줄인 2세대 14나노 핀펫 공정 LPP(Low Power Plus)를 가동하고 있다. 삼성전자는 올 하반기에 저전력, 고성능 특성을 더 높인 14나노 핀펫 LPH(Low Power High Performance) 공정을 상용화한다.

현재 파운드리 업계의 물리적 공정 전환 속도는 약 2년이다. 10나노는 인텔보다 빠르게 상용화에 성공할 것이라는 관측이다. 인텔 10나노 칩(개발 코드명 캐논레이크)은 내년에 양산이 이뤄질 예정이다. 하지만 TSMC와 삼성전자는 올 하반기에 10나노 공정을 상용화할 계획이다.

다만 파운드리 업계의 공정 전환 속도도 앞으로는 더디게 흘러갈 가능성이 크다. 최신 공정을 활용할 수 있는 시스템반도체 팹리스 업체는 애플과 퀄컴 등 손에 꼽을 정도로 적기 때문이다.

반도체 전자설계자동화(EDA) 툴 업체 시높시스의 안톤 도믹 부사장은 최근 유럽에서 개최한 디자인오토메이션&테스트 유럽(DATE) 2016 기조연설에서 “올해 초 설계를 시작한 시스템반도체 가운데 97%가 28/32나노 이전 공정을 활용하고 있다”면서 “스마트폰용 시스템온칩(SoC), 마이크로프로세서, 프로그래머블반도체(FPGA), 메모리 외에는 최첨단 공정을 활용하기 힘든 원가 구조가 됐다”고 말했다.

한주엽 반도체 전문기자 powerusr@etnews.com