삼성전자가 차세대 반도체의 구조와 소재에 대해 뚜렷한 결론을 못 내고 있다. 다만 가격·고성능을 추구했던 지금까지와 달리 저전력을 구현하는데 역량을 집중한다는 계획이다. 올해 말 양산을 계획했던 실리콘관통전극(TSV, Through-Silicon via) 반도체 상용화 시기에 대해서도 결정하지 못하고 있다.

2일 서울 양재동 엘타워에서 열린 `제2회 반도체공정장비포럼`에서 김형준 삼성전자 반도체연구소 기획지원팀 부장은 “모바일 기기가 2020년까지 100억대로 늘면 배터리 한계를 극복하고 데이터센터 전력 사용량을 줄여야 하는 두 가지 문제가 발생한다”며 “좀 더 싸고 더 빠른 성능을 구현하는 추세에서 저전력 기술의 중요성이 커지고 있다”고 말했다.

이를 위해 D램 설계는 RCAT(Recess Channel Array Transistor)와 SRCAT(Spherical Recess Cell Array Transistor), 워드라인 매립 기술인 BCAT(Buried Cell Array Transistor) 등 다양한 후보군을 검토하고 있다. 셀 구조도 VCAT, 1T-D램, STT-M램 등 여러 형태를 고민하고 있다. 캐패시터 소재를 타이타늄나이트라이드를 이용한 TIT(TiN/Insulator/TiN)에서 루테늄을 이용한 RIR(Ru/Insulator/Ru)로 전환을 검토하는 변곡점에 있다. 시스템 반도체 공정에서 쓰이는 하이케이메탈게이트(HKMG)를 메모리에 접목하는 것도 고려하고 있다.

낸드플래시는 `3D 낸드`로 불리는 V낸드 이후 3D RRAM, PRAM 등이 후보군이다.

시스템LSI의 로직 공정은 현재 20나노 양산에 들어갔고 올해 14나노 공정을 가동한다. 10나노대 이하 미세 공정을 위해 실리콘게르마늄(SiGe), 탄소기반 소재(III-V) 등을 연구하고 있고, 저전력용 금속의 k값도 2.3~2.4까지 낮출 수 있는 물질을 내년 이후 도입해야 한다. 트랜지스터 구조는 터널FET, 그래핀FET 같은 신기술을 연구 중이다.

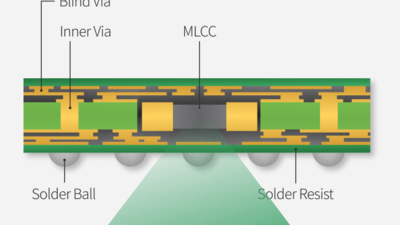

TSV는 공정 투자 대비 수익성 문제 때문에 양산 결정이 쉽지 않은 모양새다. 김 부장은 “사업부 쪽에서 검토하고 있지만 시장성에 대한 고민이 있는 것 같다”고 전했다.

오은지기자 onz@etnews.com