'2.5차원(2.5D)' 패키징의 대안 기술이 급부상했다. 2.5D는 인공지능(AI) 반도체를 구현할 핵심 기술이지만, 성능 고도화와 비용 절감 요구가 커졌기 때문이다. 특히 신호 전송 속도·효율을 극대화한 '하이브리 본딩' 기반 3차원(3D) 패키징의 확산속도가 빨리질 것이란 전망이다.

박성순 인텔 상무는 17일 전자신문과 반도체 패키징 발전전략 포럼이 공동 주최한 '반도체 한계를 넘다' 콘퍼런스에서 “첨단 패키징 기술 변화가 실리콘 인터포저를 활용하는 2.5D 패키징에서 구리 재배선(RDL) 인터포저로 대체한 2.3D 패키징, 하이브리드 본딩 3D 패키징으로 확대되고 있다”며 이같이 밝혔다.

2.5D 패키징은 실리콘 인터포저로 칩을 수평 배치하고 실리콘관통전극(TSV)으로 수직 적층하는 기술이다. AI 반도체에서 가장 많이 활용되는데, 엔비디아 AI 가속기도 이같은 구조다. 패키지 중앙에 그래픽처리장치(GPU)를 놓고 양 옆에 적층 메모리인 고대역폭메모리(HBM)를 배치한다.

2.5D 패키징을 대체하려는 요구가 크다. 실리콘 인터포저 때문이다. 실리콘 인터포저는 크기 확대가 제한적이다. 기술 난도가 높아서다. 반도체 칩 자체는 커지는데 핵심 요소인 실리콘 인터포저가 따라가지 못하는 것이다. 또 워낙 고가라 비용 부담도 크다.

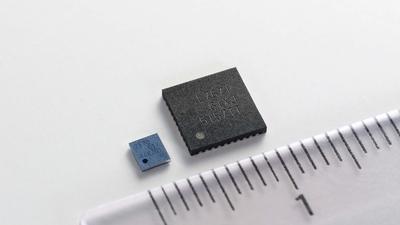

이 때문에 실리콘 인터포저 대신 RDL 인터포저를 탑재, GPU와 고대역폭메모리(HBM)을 연결하는 패키징이 급부상했다. 여기서 더 나아가 마이크로 범프를 없애고 구리와 구리를 직접 연결해 신호 전송 속도를 극대화하는 새로운 시도도 이뤄지고 있다.

박 상무는 “반도체 칩을 바로 수직으로 쌓는 3D 패키징을 하이브리드 본딩으로 구현할 수 있다”며 “하이브리드 본딩 기술이 고도화하면서 3D 패키징 확산이 빨라질 것”이라고 말했다. 박 상무는 하이브리드 본딩 기반 첨단 패키징 사례로 AMD 중앙처리장치(CPU) '라이젠'을 소개했다.

3D 패키징도 현재 2.5D처럼 TSMC가 시장 주도권을 쥘 것이란 관측도 나온다. 현재 2.5D를 통한 AI 반도체 제조는 대부분 TSMC가 맡고 있다. 다수 첨단 반도체 패키징이 TSMC에 의존하는 만큼 차세대 패키징 수요 역시 TSMC에 몰릴 것이란 관측이다. 박 상무는 “첨단 패키징에서 TSMC가 매우 중요한 역할을 하고 있다”고 부연했다.

이호길 기자 eagles@etnews.com