삼성전자가 인텔·TSMC에 대항할 차세대 반도체 패키징 기술을 개발했다. 인공지능(AI) 등 고성능 반도체를 제조하는데 쓰는 패키징 기술이다. 고객사 양산 협의할 정도로 완성도를 갖췄다. 인텔과 TSMC가 주도한 AI 반도체 산업에서 삼성이 중요 발판을 마련한 것으로 평가된다.

김구영 삼성전자 AVP(어드밴스드패키징) 공정개발팀장은 대한전자공학회, 전자신문, 차세대지능형반도체사업단 등이 공동 개최된 '반도체 패키징 발전전략 심포지엄'에서 “'아이큐브 E(I-Cube E)' 패키징을 개발했고 주요 고객사들과 양산을 준비하고 있다”고 밝혔다. 김 팀장은 “여러 주요 업체가 관심을 보이고 있다”며 “내년까지 양산 인프라를 갖출 계획”이라고 덧붙였다.

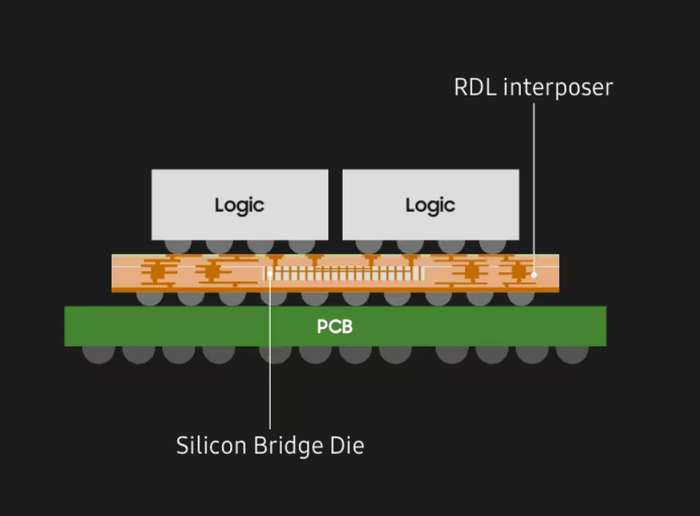

신기술(아이큐브 E)은 기존 고성능 반도체 패키징에 필요했던 '실리콘 인터포저'를 쓰지 않는 것이 핵심이다.

최근 전세계 품귀현상이 일고 있는 AI 반도체는 그래픽처리장치(GPU)와 고대역폭메모리(HBM)을 단일 반도체인 것처럼 연결해서 만든다. 대량의 데이터를 보다 빠르게 처리하기 위해 시스템 반도체와 메모리 간 경로를 최대한 좁히는 것이다.

이 때 서로 다른 반도체 칩을 붙이고, 데이터를 주고 받도록 통로 역할을 하는 것이 인터포저다. 인터포저는 실리콘을 주 재료로 사용하는데, 가격이 비싸 패키징 단가 상승의 원인으로 꼽혔다.

삼성전자는 실리콘 인터포저를 '실리콘 브릿지'로 대체했다. 반도체 전체 면적 대신 필요 부분에만 실리콘을 더하는 방식(브릿지)이다. 구체적으로 패키징에 필수적인 재배선층(RDL)에 실리콘 브릿지를 삽입(임베디드·E)한다.

삼성전자에 따르면 12개 HBM을 탑재한 반도체 칩 패키지 기준, 실리콘 인터포저를 사용한 것 대비 성능저하 없이 22% 비용을 절감할 수 있다. 삼성전자는 브릿지를 이용한 방법을 '2.3D 패키징'이라고 부른다.

브릿지 패키징은 전 세계 인텔과 TSMC가 주도했다. 인텔은 'EMIB'이라는 이름으로, TSMC는 'CoWos-L'이라는 명칭으로 실리콘 브릿지를 적용한 패키징을 양산하고 있다. 기술 상용화는 세계 1위 파운드리 업체인 TSMC보다도 인텔이 빨랐다.

삼성전자는 패키징에서 상대적으로 후발주자였는데, 이번 기술 개발로 선두 업체들과 경쟁할 무기를 마련한 것으로 평가된다. 삼성전자는 3나노, 2나노 등 최첨단 시스템 반도체를 생산할 수 있는 파운드리를 보유하고 있는 회사다. 또 AI 반도체에 필수적인 HBM 메모리를 자체 생산하고 있다. 그럼에도 AI 반도체 분야에서 큰 영향력을 발휘하지 못했는데, 첨단 패키징 기술 부재가 취약점으로 꼽혔다. 인텔은 최신 GPU '폰테베키오'를 포함한 다양한 자사 제품에, TSMC는 애플 반도체 칩에 해당 패키징 기술을 적용한 것으로 알려졌다.

삼성전자는 아이큐브 E와 같은 첨단 패키징 기술 확보를 위해 생태계 내 협력을 강화할 것이라고 강조했다.

권동준 기자 djkwon@etnews.com