국내 연구진이 세계 최고 `분자조립` 기술력으로 20㎚급 초미세패턴 구현에 성공했다.

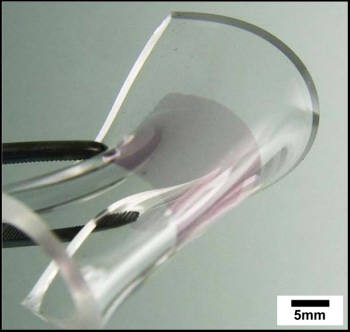

KAIST(총장 강성모)는 김상욱 신소재공학과 교수 연구팀이 유연한 그래핀 기판 위에 양산 중인 반도체 패턴의 최고 수준인 20㎚급 초미세 패턴을 구현했다고 12일 밝혔다.

이 기술 개발에는 분자가 스스로 배열하는 분자조립 기술을 활용했다. 분자조립은 플라스틱, 액정, 생체분자 등과 같이 딱딱하지 않고 유연한 연성소재 고분자를 원하는 형태로 스스로 배열하게 해 기존에 만들기 어려웠던 작은 나노구조물을 효율적으로 만드는 기술이다. 서로 다른 두 고분자가 물과 기름처럼 서로 섞이지 않는 점을 이용한다.

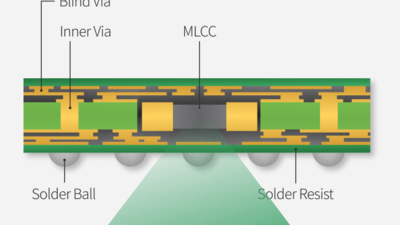

연구진은 그래핀 위에 `블록공중합체`라는 분자조립 기술을 이용해 초미세 패턴을 형성한 후 이를 3차원 기판이나 PET(폴리에틸렌테레프탈레이트), PDMS(폴리디멜틸실론산) 등과 같은 플렉시블 기판에 옮겨 자유롭게 구조물을 만들었다.

유연하게 휘어지면서도 많은 양의 데이터를 저장할 수 있는 반도체 제조의 길이 열린 셈이다. 연구진은 고성능 플렉시블 전자기기 개발에 도움이 될 것으로 기대했다.

연구진은 연성소재 특성을 이용해 초미세 패턴을 형성하기 어려운 3차원의 굴곡진 기판에 자유롭게 구현하는 데도 성공, 반도체 제작비용이 저렴해질 것으로 전망했다. 이 방법은 다양한 응용소자 활용은 물론이고 화학 반응으로 물질을 섞어주기만 하면 원하는 형태로 패턴을 스스로 배열하기 때문에 고가의 장비가 필요 없다.

김상욱 교수는 “지금까지 발표된 휘어지는 반도체는 온도에 취약한 플라스틱 기판을 사용해 극한 공정조건을 극복해낼 수 없어 상용화에 어려움이 많았다”며 “기계적 물성이 우수한 그래핀을 회로 기판으로 적용하는 데 성공한 획기적 연구 성과”라고 말했다.

이 연구 성과는 교육과학기술부 글로벌프런티어사업 다차원 스마트 IT 융합시스템 연구단의 지원을 받아 수행됐다. 재료분야 국제 학술지 `어드밴스트 머티리얼스(Advanced Materials)` 3월 6일자에 게재됐다.

대전=박희범기자 hbpark@etnews.com