3차원 집적회로(3D IC)의 집적화가 급격히 진화하고 있다.

전문가들은 칩의 집적도가 18개월마다 배로 증가한다는 ‘무어의 법칙’을 넘어설 기세라고 입을 모았다.

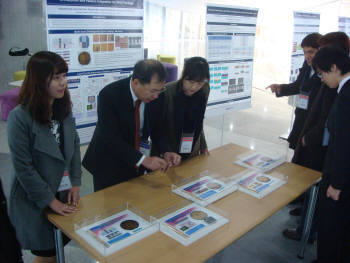

KAIST가 지난 7일 교내 KI빌딩에서 개최한 ‘3D IC 워크숍 2011’에서는 반도체, 패키지 관련 업체 및 연구기관 관계자 300여 명이 몰려 ‘3D IC’에 뜨거운 관심을 드러냈다. 이 행사에는 삼성전자와 앰코, 동부하이텍, 하이닉스반도체, 한국전자통신연구원(ETRI), 전자부품연구원(KETI), 나노종합팹센터, 충북대, 한국과학기술원(KAIST), 폴리오그 등 국내 반도체 및 패키지 업계와 연구기관 연구원들이 참여했다.

이날 가장 큰 화두는 ‘실리콘 관통 전극(TSV) 기반의 3D IC’였다. 국내에서는 세계적인 수준에 올라 있는 김정호 KAIST 전기 및 전자공학과 교수 연구팀이 독보적인 위치를 점하고 있다.

이춘흥 앰코 전무는 “2009년 325만달러 규모의 3D IC 시장이 2015년 4억1500만달러 규모까지 급격히 증가할 것”으로 전망했다.

이희석 삼성전자 박사는 “3D IC에서 사용되는 TSV를 이용한 전기적 배선은 기존의 와이어 본딩이나 플립칩보다 길이가 짧고 IC 내부에서 더 적은 면적을 차지하기 때문에 매우 우수한 성능의 시스템 설계가 가능하다”며 “전력 소모도 기존보다 50% 가까이 줄일 수 있다”고 주장했다.

이한춘 동부하이텍 수석연구원은 “무어의 법칙을 넘어서기 위한 미래 기술이 바로 TSV를 이용한 3D IC 기술”이라며 “앞으로는 시스템 반도체 기술의 고성능화와 고집적화에 가속도가 붙을 것”이라고 설명했다.

김정호 KAIST 교수는 “TSV를 이용한 고속 신호전송선 설계기술이 반드시 확보돼야 높은 대역폭을 요구하는 그래픽 메모리나 영상분야, 그리고 저전력이 필요한 모바일 스마트폰을 구현할 수 있을 것”으로 내다봤다.

대전=박희범기자 hbpark@etnews.co.kr