휴대전화나 디지털카메라 등의 보드 크기를 획기적으로 줄일 수 있는 친환경적 차세대 반도체 패키지 기술(SiP)이 상용화 수준으로 국내에서 처음 개발됐다.

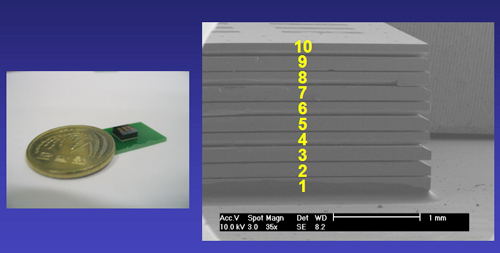

한국과학기술원(KAIST) 전자패키지재료연구센터(소장 유진)는 다기능 반도체 칩과 부품을 3차원으로 10개 층까지 쌓을 수 있는 차세대 패키지 기술을 국내 처음 개발하는 데 성공했다고 15일 밝혔다.

이 기술 개발에는 서울대·연세대·한양대·홍익대·포스텍·한밭대 등 모두 7개 대학 16명의 교수진과 50여명의 연구인력이 참여했다.

신기술은 반도체 칩에 50㎛ 크기로 구멍을 뚫어 상호 수직 연결하는 관통전극기술을 채택, 가로 5㎜, 세로 5㎜ 크기의 칩을 최대 10개 층까지 쌓아 보드 면적을 기존보다 40∼50% 줄인 것이 가장 큰 특징이다.

SiP는 납을 사용하지 않는 무연솔더 접합기술(레드 프리)을 적용한 친환경 그린 패키지로 개발, EU가 내년 7월부터 전자제품에 납이나 카드뮴, 수은 등 6개 중금속을 위험한 물질로 묶어 수출입을 제한하는 ‘RoHS’ 규정을 충족시킨다.

그동안 일부 국내 대기업은 휴대전화나 PDA, 디지털카메라, 노트북PC, 이미지 센서 등 반도체 칩의 크기를 줄이기 위해 SiP 개발에 전력투구해 왔으며 삼성전자가 최근 8개의 칩을 와이어 본딩법으로 적층한 바 있다.

유진 소장은 “내달부터 관통전극을 10㎛로 줄이는 연구가 진행된다”며 “10년 뒤에는 가로, 세로 1㎜의 면적에 온갖 기능을 담은 칩이 의료용 로봇이나 바이오에 활용될 것”이라고 말했다.

대전=박희범기자@전자신문, hbpark@