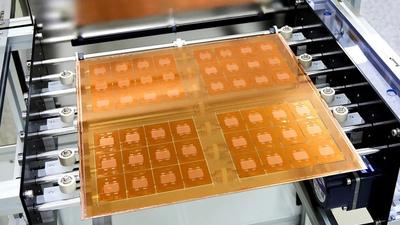

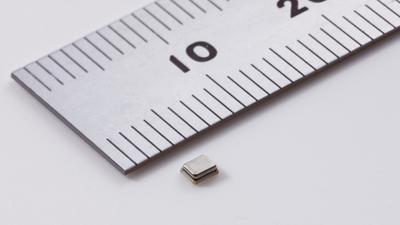

초당 1조번의 온(on) 오프(off) 작동을 수행할 수 있는 트랜지스터 구조가 개발됐다.

외신에 따르면 인텔은 기존 SOI에 비해 전류의 방출을 100분의 1 이하로 줄여 트랜지스터의 소비 전력은 줄이고 성능은 높일 수 있는 새 SOI(Silicon On Insulator) 기술과 이를 적용한 트랜지스터 구조를 개발했다.

이 기술을 마이크로프로세서에 적용할 경우 실시간 음성 및 얼굴 인식 등의 애플리케이션이 가능해지며 컴퓨터의 크기를 크게 줄이고 배터리 사용시간은 획기적으로 늘릴 수 있다.

인텔의 새 SOI 기술은 DST(Depleted Substrate Transistor)를 이용해 트랜지스터 실리콘층의 두께를 줄이고 웨이퍼상의 실리콘 이산화물을 신물질로 대체해 트랜지스터의 전류 방출을 억제하는 기술이다. 트랜지스터에서 방출되는 전류는 전력 소모의 대부분을 차지할 뿐 아니라 마이크로프로세서의 데이터 에러를 유발하고 많은 열이 발생해 실리콘을 녹인다.

인텔측은 DST 기술을 적용해 부분적인 DST를 사용하는 IBM 등의 기존 SOI에 비해 전류 방출량을 100분의 1로 줄였다고 주장했다. 그러나 인텔은 실리콘 이산화물을 대체한 신물질은 공개하지 않았다.

이와 관련, 시장조사기관인 VLSI리서치의 분석가인 댄 허치슨은 “새 트랜지스터 기술은 기본적으로 (기존 SOI와) 다르며 실제 제작이 가능한 기술”이라며 “인텔이 트랜지스터의 리엔지니어링을 끝마쳤다”고 평가했다.

인텔의 기술 및 제조그룹의 부품연구담당 이사인 제럴드 마사익은 “새기술을 통해 프로세서의 트랜지스터 집적도를 25배 늘려 전력 소모는 그대로 유지한 체 성능만 10배 늘릴 계획”이라고 말했다.

인텔은 이번에 개발한 새 트랜지스터의 구조를 2005년에 마이크로프로세서에 적용하기 시작할 방침이다.

인텔은 새 트랜지스터의 자세한 내용을 내달 3일 워싱턴에서 개최되는 국제전자디바이스회합(IEDM)에서 공개할 예정이다.

<황도연기자 dyhwang@etnews.co.kr>

국제 많이 본 뉴스

-

1

모토로라 중저가폰 또 나온다…올해만 4종 출시

-

2

단독개인사업자 'CEO보험' 가입 못한다…생보사, 줄줄이 판매중지

-

3

LG엔솔, 차세대 원통형 연구 '46셀 개발팀'으로 명명

-

4

역대급 흡입력 가진 블랙홀 발견됐다... “이론한계보다 40배 빨라”

-

5

LG유플러스, 홍범식 CEO 선임

-

6

5년 전 업비트서 580억 암호화폐 탈취…경찰 “북한 해킹조직 소행”

-

7

반도체 장비 매출 1위 두고 ASML vs 어플라이드 격돌

-

8

페루 700년 전 어린이 76명 매장… “밭 비옥하게 하려고”

-

9

127큐비트 IBM 양자컴퓨터, 연세대서 국내 첫 가동

-

10

'슈퍼컴퓨터 톱500' 한국 보유수 기준 8위, 성능 10위

브랜드 뉴스룸

×

![]()