내년 말 양산…공급망 구축 착수

셀·페리 웨이퍼 두 장 연결·부착

하이브리드 본딩, 적층한계 돌파

SK하이닉스가 낸드플래시 적층 한계 돌파에 착수했다. 반도체 웨이퍼 두장을 이어 붙이는 차세대 패키징 기술로 내년 400단대 낸드플래시 메모리를 개발한다는 계획을 세운 것으로 파악됐다. SK하이닉스는 양산 기술까지 확보할 방침으로, 관련 소재·부품·장비(소부장) 공급망 구축에 착수했다.

30일 업계에 따르면 SK하이닉스는 400단급 낸드플래시 메모리 개발에 착수했다. 이 사안에 정통한 업계 관계자는 “SK하이닉스가 소부장 협력사와 400단 이상 낸드를 위한 공정 기술과 장비를 개발하고 있다”며 “내년 말 양산이 가능한 수준으로 기술과 인프라를 갖추는 것이 목표”라고 밝혔다.

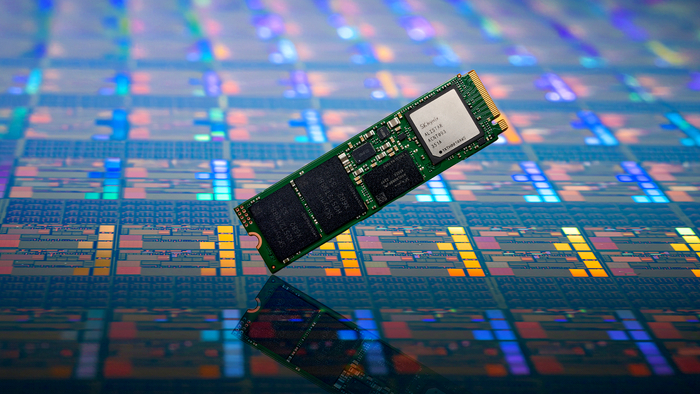

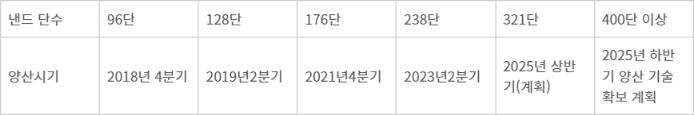

낸드플래시는 데이터를 저장할 수 있는 메모리 반도체다. 저장공간인 셀을 여러 층으로 쌓으면 낸드의 저장용량이 늘어난다. 400단은 현존 낸드의 최고 수준인 321단을 훨씬 뛰어넘는 것으로, SK하이닉스의 차세대 낸드 양산 계획이 파악된 건 처음이다.

SK하이닉스는 '하이브리드 본딩'으로 400단대 낸드를 구현할 계획인 것으로 파악됐다. 구체적으로 하이브리드 본딩 중 웨이퍼와 웨이퍼를 맞붙이는 '웨이퍼 투 웨이퍼(W2W)' 기술을 적용할 방침이다.

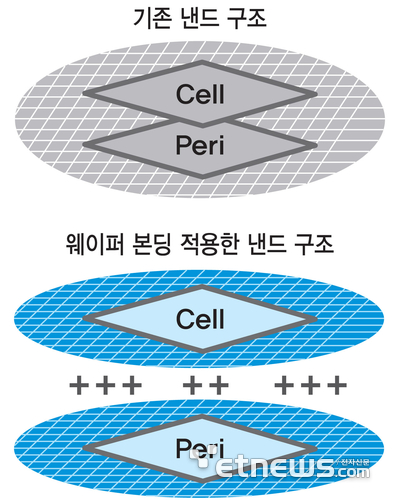

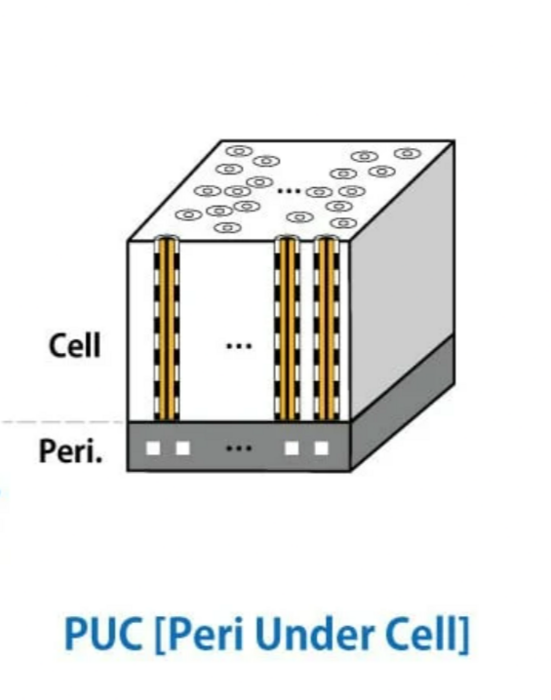

지금까지 SK하이닉스는 낸드 플래시 데이터를 저장하는 영역 '셀'과 이를 구동하는 회로 영역인 '페리페럴(페리)'을 한장의 웨이퍼에서 구현했다.

페리 위에 셀을 적층하는 형태로 '페리언더셀(PUC)'이라고 부른다. 주상복합 아파트처럼 페리(상가)를 아래에 두고 셀(주거지)을 얹은 형태다.

삼성전자 역시 비슷한 구조(셀온페리: COP)로 낸드를 구현한다. 한 번에 셀을 쌓느냐 두 번에 걸쳐 쌓느냐에 따라 '원스택', '더블스택' 으로 구분한다.

그러나 낸드 단수가 높아지면서 셀 아래에 페리를 두는 것은 한계에 직면했다. 셀을 쌓는 과정에서 페리가 손상되기 때문이다. 셀 공정에서 발생하는 높은 열과 압력을 견디지 못한 탓이다.

이를 극복할 기술이 바로 하이브리드 본딩이다. 셀과 페리를 서로 다른 웨이퍼에서 구현한 후 두 장의 웨이퍼를 다시 붙여서 초고단 낸드를 만들어내는 방식이다. 이 경우 셀을 400단 이상으로 쌓고, 셀을 구동할 페리 웨이퍼는 따로 제조할 수 있어 안정적으로 낸드 단수를 높일 수 있다. SK하이닉스는 이같은 장점에 400단 이상 낸드 제조에 W2W 방식 도입을 결정한 것으로 전해졌다.

이같은 SK하이닉스의 하이브리드 본딩 도입으로 낸드 제조 공정에 대대적인 변화가 예상된다. 반도체 소부장 업계 관계자는 “하이브리드 본딩 자체가 첨단 패키징 영역인 만큼, 많은 패키징 소부장 업체가 SK하이닉스 낸드 공급망에 진입하게 될 것”이라고 밝혔다.

실제 SK하이닉스는 소부장 공급망에도 변화를 주는 것으로 파악됐다. 하이브리드 본딩을 위한 접합 소재부터 각기 다른 웨이퍼를 연결하기 위한 연마·식각·증착·배선 기술을 신규 검토 중이며, 계측·검사까지 새로운 소재·장비 도입을 추진하고 있다. 내년 말까지 양산 기술을 확보한다는 목표인 만큼 2026년 상반기 중 본격 생산이 예상된다.

세계 최대 낸드플래시 생산 업체인 삼성전자도 400단대 낸드를 개발 중이어서 치열한 상용화 경쟁이 불붙을 전망이다. 삼성전자 역시 하이브리드 본딩을 차세대 낸드에 적용하는 방안을 검토 중인 것으로 알려졌다.

SK하이닉스 측은 낸드플래시 생산과 관련해 “당사 기술 개발이나 양산 시점에 대해서는 확인해 줄 수 없다”고 밝혔다.

권동준 기자 djkwon@etnews.com