한국과학기술원(KAIST) 반도체설계교육센터(IDEC·소장 경종민 교수)는 반도체 시제품 제작 서비스 기간을 3개월 단축하기로 했다고 6일 밝혔다.

‘멀티프로젝트웨이퍼(MPW)’라고도 불리는 이 서비스는 한 웨이퍼에 여러 종류의 칩을 함께 제작함으로써 많은 설계자가 저렴한 비용으로 칩을 제작할 수 있는 방식. IDEC는 96년부터 ‘반도체설계공모전’에 참가하는 60여개의 대학 및 연구소를 대상으로 6개월 기간의 서비스를 제공해왔다.

IDEC는 올해 삼성전자·하이닉스반도체·아남반도체·ETRI·동부전자를 통해 0.35∼0.18㎛ CMOS 공정과 0.5㎛ MES FET공정, 0.25㎛ PHEMT 공정 등에서 총 240여종의 칩 제작서비스를 지원할 예정이다.

<정지연기자 jyjung@etnews.co.kr>

전자 많이 본 뉴스

-

1

전자 소자·부품도 공급망 경고등…고사양 콘덴서 공급 20주 넘게 밀린다

-

2

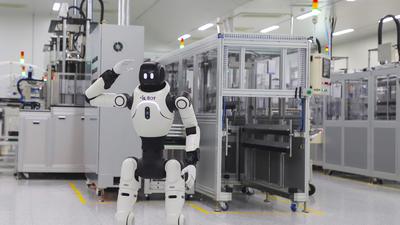

두산로보틱스-엔비디아, 피지컬 AI 로봇 협력…2028년 산업용 휴머노이드 선보인다

-

3

삼성전자 “HBM4, 3분기 메모리 매출 과반 예상”

-

4

삼성전기, 2026년 1분기 영업이익 2806억원…전년比 40%↑

-

5

삼성중공업, 1분기 영업이익 2731억원…전년比 122%↑

-

6

LG에너지솔루션, 1분기 매출 6조5550억·2078억 손실 기록

-

7

국내 최초 휴머노이드 로봇 쇼룸 문 연다…로봇이 춤추고 커피도 내려

-

8

2026 월드컵 겨냥…삼성전자, AI TV 보상판매 프로모션

-

9

삼성전자, 1분기 반도체 영업이익 53.7조원… “2분기도 호실적”

-

10

삼성전자, 인도서 '파이낸스 플러스' 할부 서비스 출시…“제품 접근성 향상”

브랜드 뉴스룸

×

![]()