국내 최초로 30나노미터(㎚)급 나노 CMOS 소자가 개발돼 테라급 반도체 상용화에 대한 기대를 높이고 있다.

서울대학교 전기컴퓨터공학부 ‘반도체 소자 및 재료 연구실’은 30㎚의 극소 게이트 선폭을 갖는 전계효과트랜지스터(MOS FET)를 개발하는 데 성공했다고 7일 발표했다.

연구팀은 기존 노광(리소그래피)장비로 형성한 패턴의 가장자리를 따라가면서 30㎚의 층을 쌓은 뒤 나머지 부분을 제거하는 측벽(side wall) 패터닝 기술과 급속열산화(RTO)장비를 이용한 1㎚ 극박막 산화막 형성기술을 적용했다고 밝혔다.

이번 개발을 주도한 박병국 교수는 “기존 평면형(planer) 소자 구조의 연장선상에서 전통적 양산공정을 활용해 만들었기 때문에 양산화가 쉽다는 것이 가장 큰 장점”이라며 “5∼6년 안에 테라비트급 초고집적 소자의 상용화가 가능할 것”이라고 전망했다.

현재 양산중인 집적회로 소자의 최소 선폭은 130㎚급이며 30㎚ 선폭을 가진 나노 CMOS 소자가 상용화되면 D램 용량 기준으로 1테라비트(1000기가비트)급 소자 제작이 가능하다.

전세계적으로 반도체 용량의 한계를 뛰어넘기 위한 나노급 소자 개발경쟁이 치열한 가운데 지난해 6월 인텔이 20㎚급 트랜지스터를 발표했으며 국내에서는 98년 KAIST가 50㎚급 실리콘온인슐레이터(SOI) 트랜지스터를 선보인 바 있다.

<정진영기자 jychung@etnews.co.kr>

많이 본 뉴스

-

1

“저녁 대신 먹으면 살 쭉쭉 빠진다”···장 건강·면역력까지 잡는 '이것' 정체는?

-

2

“라면 먹을떄 '이것' 같이 먹지 마세요”…혈관·뼈 동시에 망가뜨려

-

3

의사가 극찬한 '천연 위고비'…“계란 먹고 살찌는 건 불가능”

-

4

배달 3사, 이번엔 '시간제한 할인' 경쟁…신규 주문 전환율 높인다

-

5

현대차, '더 뉴 그랜저' 디자인 공개…“新기술 집약”

-

6

中 BYD, 국내에 첫 하이브리드차 출시…전기차 이어 포트폴리오 다각화

-

7

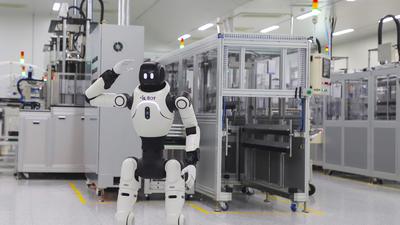

국내 최초 휴머노이드 로봇 쇼룸 문 연다…로봇이 춤추고 커피도 내려

-

8

'HMM 부산 이전' 李대통령 “약속하면 지킨다…이재명은 했다”

-

9

삼성바이오 전면파업 이틀째…5일까지 총파업 강행

-

10

우리은행, 계정계 '리눅스 전환' 착수…코어 전산 구조 바꾼다

브랜드 뉴스룸

×

![]()