과기처는 그동안 2백56메가D램 제품 개발 중심으로 추진해온 차세대 반도 체개발사업을 1기가 D램급 이상 제품 개발을 위한 기반기술 확보 중심으로 대폭 전환하기로 했다. 과기처는 또한 97년말까지 12인치 웨이퍼의 엔지니어 링샘플도 개발하기로 했다.

과기처는 23일 열린 차세대 반도체연구개발사업 조정위원회에서 최근 반도체3사의 2백56메가 D램의 워킹샘플 개발을 계기로 차세대 반도체 사업의 개발목표를 2백56메가 D램에서 1기가 D램 이상 중심으로 상향조정하는 내용의차세대 반도체 기반기술 개발사업 보완계획을 보고해옴에 따라 다음달초 정부안으로 이를 확정、 적극 추진키로 했다.

이와 관련、 사업단은 3.4차연도 단위공정 연구비를 당초 전체투자비의 76 %인 8백6억원에서 32.9%인 3백49억원으로 대폭 축소、 이를 선행연구 부문에투입하기로 했다.

이에 따라 2백56메가 D램 중심으로 개발해온 패터닝기술 개발계획을 조기에종료하고 차세대 리소그라피 기술개발을 신규과제로 추가、 기업주도로 개발하기로 했다.

또한 선행기초기술 확대를 위해 기업주도의 선행기초과제를 선정、 전체연구비의 37%인 3백94억원을 지원하고 대학이나 연구소에 대한 연구비지원도 30억원정도 늘리기로 했다.

재료기술개발과 관련해서는 이 기간중 재료기술분야에 대한 연구비규모를 기존 48억원에서 80억원으로 70% 가량 상향조정하는 한편 현재 8인치 웨이 퍼개발 중심을 12인치 개발중심으로 변경、 내년까지 8인치 웨이퍼 개발을 완료하는 한편 97년까지 12인치 웨이퍼의 엔지니어링 샘플도 개발하기로 했다. 사업단은 그러나 장비개발에 대해서는 현행 장비당 32억2천만원의 연구비 가충분하다고 판단、 예정대로 진행하기로 했으며 스테퍼의 개발은 국내 산 업여건상 시기상조라고 판단、 중단하기로 했다.

한편 이같은 보완계획은 다음달초 정부 부처간 협의를 거쳐 정부안으로 최종확정될 예정인데, 1기가 D램 이상의 기반기술 확보계획은 미 일 독 3국이 1기가 D램의 공동개발에 나선 시점에 나온 것이어서 특히 주목된다.

<이창호 기자>

많이 본 뉴스

-

1

“저녁 대신 먹으면 살 쭉쭉 빠진다”···장 건강·면역력까지 잡는 '이것' 정체는?

-

2

“라면 먹을떄 '이것' 같이 먹지 마세요”…혈관·뼈 동시에 망가뜨려

-

3

의사가 극찬한 '천연 위고비'…“계란 먹고 살찌는 건 불가능”

-

4

배달 3사, 이번엔 '시간제한 할인' 경쟁…신규 주문 전환율 높인다

-

5

현대차, '더 뉴 그랜저' 디자인 공개…“新기술 집약”

-

6

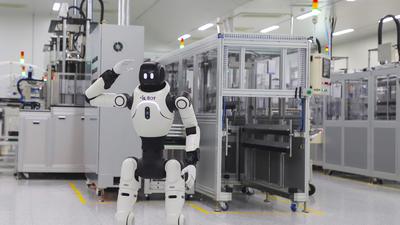

국내 최초 휴머노이드 로봇 쇼룸 문 연다…로봇이 춤추고 커피도 내려

-

7

中 BYD, 국내에 첫 하이브리드차 출시…전기차 이어 포트폴리오 다각화

-

8

삼성바이오 전면파업 이틀째…5일까지 총파업 강행

-

9

'HMM 부산 이전' 李대통령 “약속하면 지킨다…이재명은 했다”

-

10

우리은행, 계정계 '리눅스 전환' 착수…코어 전산 구조 바꾼다

브랜드 뉴스룸

×

![]()