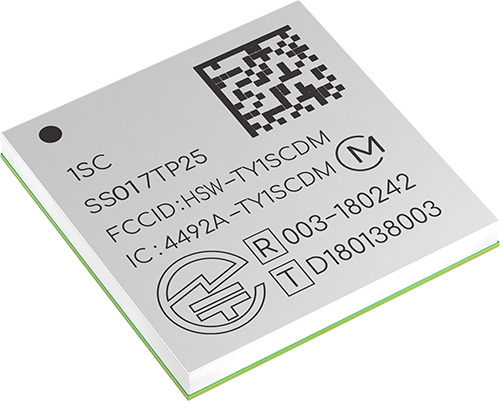

키옥시아와 웨스턴디지털은 6세대 162단 3D 플래시 메모리 기술을 개발했다고 24일 발표했다.

이번에 발표된 6세대 3D 플래시 메모리는 전작인 5세대 제품보다 10% 증가한 측면 셀 어레이 밀도가 특징이다.

측면 미세화로 162단 수직 적층 메모리와 결합해, 112단 적층 기술 대비 40% 감소된 칩 크기를 구현했다.

양사는 6세대 3D 플래시 메모리에 '서킷 언더 어레이' CMOS 배치와 '4플레인' 방식을 함께 적용해 이전 세대 대비 2.4배가량 향상된 프로그램 성능과 10%의 읽기 지연 시간 개선을 달성했다. 입출력(I/O) 성능 또한 66% 향상시켰다.

또 웨이퍼당 비트 생산이 이전 세대보다 70% 증가해 비용이 절감됐다.

시바 시바람 웨스턴디지털 기술 및 전략 부문 사장은 "이번 6세대 플래시 기술로 키옥시아와 웨스턴디지털은 보다 작은 크기의 다이와 적은 수의 단으로도 한층 높은 용량을 달성할 수 있는 기술을 선보였다"고 밝혔다.

강해령기자 kang@etnews.com