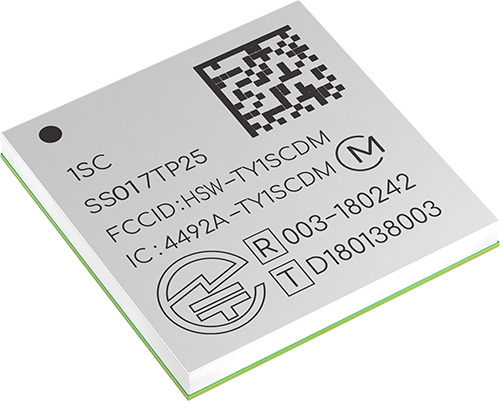

삼성전자가 10나노미터(㎚)급 초미세 공정을 이용한 낸드플래시 반도체를 이르면 2012년 양산한다. 또 D램 반도체에서는 2014년께 10㎚ 공정을 활용한 제품을 선보일 계획인 것으로 확인됐다.

특히 반도체 전문가들이 30㎚ 공정을 D램 반도체의 한계로 지적했으나 문 전무는 수 나노까지 개발할 수 있다고 밝혀 관심이 집중된다.

문주태 삼성전자 전무는 3일 서울 코엑스에서 개막한 ‘세미콘코리아 2010’ 기조연설을 통해 “10㎚ 초미세공정을 위한 패터닝 기술 장벽이 점점 사라지고 있다”며 “낸드플래시의 경우 2012년께 10㎚ 공정을 활용한 제품이 선보일 수 있을 것”이라고 전망했다.

삼성전자 반도체연구소 공정개발팀을 맡고 있는 문 전무의 이 같은 전망은 삼성전자가 D램 및 낸드플래시 공정기술을 선도하고 있다는 점에서 이 회사의 양산 목표로 분석됐다. 특히 삼성전자가 반도체 소형화 및 신시장 개척을 위한 기술적 청사진을 이미 완성한 것으로 해석됐다.

문 전무는 “D램의 경우 2014년께 버티컬 채널 트랜지스터(VCT) 기술을 통해 회로 집적도를 크게 향상시킬 수 있을 것”이라며 “극자외선(EUV) 패터닝 장비 상용화와 맞물려 초미세공정을 통한 반도체 고집적화에 새로운 차원이 열릴 것”이라고 전망했다. VCT 기술은 반도체 소자를 여러 겹의 수직으로 패터닝하는 기술로 공정 및 장비 개발이 한창이다.

문 전무는 낸드플래시의 경우 10㎚급 제품의 상용화 시기가 더 빠를 것이라고 전망했다. 그는 “낸드플래시의 경우 현재의 평면 셀 기술이 3차원 구조를 갖춘 셀 기술로 전환하면서 고집적 한계를 극복할 수 있을 것”이라며 “이르면 2012년 10㎚급의 제품이 출현할 것”이라고 말했다. 문 전무는 오는 2016년 경에는 수 나노급 낸드 플래시가 출시될 것으로 예측했다.

문주태 전무는 또 “웨이퍼 사이즈를 키우는 게 가격 절감의 가장 큰 이슈”라며 “이르면 2012년 4500㎜ 웨이퍼 기반의 팹이 출현하고, 2015년께 주력 웨이퍼 표준으로 부상할 것”이라고 전망했다.

반도체 시장 성장에 대해서는 “개발도상국의 급격한 수요 증가와 바이오, 나노, 로보틱스 산업이 미래 반도체의 새로운 성장엔진이 될 것”이라며 “신시장의 경우 2015년께 본격적인 개화기를 맞을 것”이라고 덧붙였다.

양종석기자 jsyang@etnews.co.kr

전자 많이 본 뉴스

-

1

'게임체인저가 온다'…삼성전기 유리기판 시생산 임박

-

2

LS-엘앤에프 JV, 새만금 전구체 공장 본격 구축…5월 시운전 돌입

-

3

'전고체 시동' 엠플러스, LG엔솔에 패키징 장비 공급

-

4

브로드컴 “인텔 칩 설계사업 인수 관심 없어”

-

5

LG전자, 연내 100인치 QNED TV 선보인다

-

6

필에너지 “원통형 배터리 업체에 46파이 와인더 공급”

-

7

램리서치, 반도체 유리기판 시장 참전…“HBM서 축적한 식각·도금 기술로 차별화”

-

8

필옵틱스, 유리기판 '싱귤레이션' 장비 1호기 출하

-

9

소부장 '2세 경영'시대…韓 첨단산업 변곡점 진입

-

10

비에이치, 매출 신기록 행진 이어간다

브랜드 뉴스룸

×

![]()