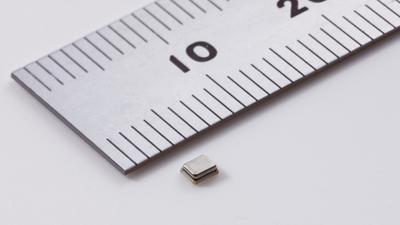

일본 후지쯔와 후지쯔연구소가 주메모리에 사용되는 D램의 고속데이터전송을 실현하는 회로를 개발했다고 일본 「日經産業新聞」이 최근 보도했다.

이에 따르면, 후지쯔는 클럭신호 위상을 잘게 분할해 조정하는 방법으로 신호 타이밍을 보다 정확히 맞추는 동시에 반복 간격이 짧은 고주파수 클럭신호에 대응할 수 있는 새로운 디지털동기(同期)회로를 고안했다.

이번에 개발된 회로를 D램 입출력부에 사용하면 지금까지 D램에서는 실현할 수 없었던 1백25-4백MHz의 고속데이터 입출이 가능하다. 마이크로프로세서(MPU)의 경우는 이미 동작속도 2백66MHz 제품이 실용화돼 있지만 동기회로가 부착돼 있지 않은 기존 D램은 데이터전송속도 1백MHz가 한계이다.

새 회로는 또 대기 전력을 종래의 1백분의 1수준으로 억제할 수 있어 노트북PC, 휴대정보단말기(PDA) 등에 이용할 수 있다.

현재 MPU 등에 내장돼 있는 동기회로는 데이터 입출력이 없는 대기시 전류가 1백마이크로A 이상 필요한데, 이를 이용하면 D램 전체의 대기전류는 1백50마이크로A 이상이 된다. 반면에 새 회로는 1.4마이크로A면 충분하고, D램 전체로도 50마이크로A정도면 된다.

<신기성기자>

국제 많이 본 뉴스

-

1

내년 '생성형 AI 검색' 시대 열린다…네이버 'AI 브리핑' 포문

-

2

5년 전 업비트서 580억 암호화폐 탈취…경찰 “북한 해킹조직 소행”

-

3

LG이노텍, 고대호 전무 등 임원 6명 인사…“사업 경쟁력 강화”

-

4

AI돌봄로봇 '효돌', 벤처창업혁신조달상품 선정...조달청 벤처나라 입점

-

5

롯데렌탈 “지분 매각 제안받았으나, 결정된 바 없다”

-

6

애플, 'LLM 시리' 선보인다… “이르면 2026년 출시 예정”

-

7

'아이폰 중 가장 얇은' 아이폰17 에어, 구매 시 고려해야 할 3가지 사항은?

-

8

美-中, “핵무기 사용 결정, AI 아닌 인간이 내려야”

-

9

삼성메디슨, 2년 연속 최대 매출 가시화…AI기업 도약 속도

-

10

美 한인갱단, '소녀상 모욕' 소말리 응징 예고...“미국 올 생각 접어”

브랜드 뉴스룸

×

![]()