로버트A.크레이븐 45년 매사추세츠주 출생 <>트리니티대 졸업 <>로체스터대학원 석사 및 박사학위 취득 <>IBM왓슨연구소 연구원 <>MEMC일렉트로닉 머티리얼즈사 마케팅 부사장 <>현 사이본드(SiBond L.L.C) 사장 SOI(silicon on silicon)에 관한 연구는 지난 수년간 꾸준히 진행되어 왔으며 최근에는 SOI 기판이용으로 극적인 디바이스 성능향상이 가능함을 보여주는 많은 보고서들을 볼 수 있다. 오늘날 SOI의 이용분야로는 아날로그 및복합신호 그리고 스마트 전력소자등의 응용을 들 수 있다.

CMOS/SOI구조는 근본적으로 두가지 선택이 있다.

첫번째 선택은 완전공핍화라는 구조이며 이는 <그림1> 과같이 SOI층의 두께가 디바이스 채널 영역내 공핍층 넓이보다 얇은 경우에 해당한다.

이러한 구조하에서는 게이트에 전압을 추가로 인가하게 되면 반도체의 공핍 화가 더 이상 일어나지 않기 때문에 채널 반전 캐리어와 드레인 전류가 증가 한다. 그 결과 문턱이하(subthreshold) 역기울기가 이상적인 값인 6mV 데케이드에 접근하게 되어 트랜지스터의 sharp turn on이 가능하게 된다. 그외에소스와 드레인 접합영역에서도 기판의 공핍화가 산화층에 의하여 방지된다.

따라서 소스및 드레인과 기판 사이의 축전용량이 매립산화층의 그것으로 대치되어 전형적으로 벌크 실리콘기판 통상 용량의 25% 혹은 그 이하가 된다.

두번째 선택으로는 부분 공핍화 SOI라고 부르는 디바이스이며 이는 <그림2> 에서 묘사한 바와 같이 보다 전통적인 MOS트랜지스터 구조와 유사하다. 이러한 구조에서는 문턱전압이 SOI 두께에 극히 민감하지는 않다. 그러나 게이트 아래에 중립상태의 실리콘 본체가 잔존하며, 이는 벌크 실리콘 경우와는 달리 부유한다. 이 부유 실리콘 본체는 특수본체 접촉을 이용함으로써 결집시킬 수는 있다. 이 결과 공핍용량 C 가 완전공핍화 경우만큼 감소되지는 않는다. 이러한 디바이스는 사실상 벌크 실리콘 설계에 요구되는 모든 특징들 에 편승하고 있다.

디바이스 성능면에서 볼 때 SOI/CMOS는 몇가지 즉각적인 이점들을 제공한다.

예를들면 먼저 SOI/CMOS를 사용함으로써 작동온도를 내리지 않고도 문턱전압을 효과적으로 낮출 수 있는 방법이 제공된다. 높은 드라이브 전류에 의하여 스위칭 트랜전트를 가속시킴으로써 성능향상을 가져온다. 벌크 실리콘과 비교할 때 작동전압을 내릴 수 있으며 고성능 수준의 작동이 가능하다. SOI 회로의 고유한 장점인 낮은 누설전류와 더불어 저전력회로의 달성이 용이한 이러한 부분공핍화 접근방식은 널리 관심을 끌고 있으며 SOI제품을 디바이스 설계에 적극적으로 이용하는 기술원동력 중 하나이다. 완전공핍화 디바이스 구조 설명시 언급한 기생용량 감소 또한 중요한 인자이며, 부분공핍화디바이스에서도 기생용량 감소 효과가 있어 성능향상에 30%정도 기여한다.

SOI의 다른 응용분야로서 방사선 면역증가 SOI회로 및 BiCMOS 응용을 들 수있다. 이중 BiCMOS 응용에서는 SOI를 사용함으로써 바이폴라회로의 집적을 보다 쉽게 할 수 있는 가능성이 커진다. 이러한 응용에서는 SOI재료의 우수 한 소수 캐리어 수명이 요구되며 따라서 이온주입 기술보다도 본디드 SOI기 술이 더 선호되고 있다.

성능면이외 SOI실행의 원동력은 원가이다. SOI를 사용한 공정의 간편화에 관한 세부적인 연구들을 보면 주로 격리 scheme의 간편화에 줄기를 두고 있다.

예를들면 여러가지 웰(well)주입공정의 제거와 특정 디바이스들을 래치 업 문제의 우려없이 서로 가깝게 위치시킬 수 있는 능력에 의하여 공정의 복잡 성을 감소시킬 뿐만 아니라 다이 크기도 의미있는 수준으로 감소시킬 수 있다. 소니의 니시하라등이 제시한 바와 같이 SOI를 이용한 혁신적 다층구조는 D램 구조 개발에 있어서 디바이스 축소를 더욱 극적으로 달성할 수 있는 기회를 제공한다. 이러한 방식의 셀설계는 리드(read) 트랜지스터 및 저장노드의 수직적인 적층을 가능하게 한다. 그 결과 셀 치수의 축소는 지금까지 즉 64Mb 세대까지 달성해왔던 0.4×1세대의 메모리 스케일링 경향이 지속될 수 있도록 해준다. 한편 얇은 Si층내에 트랜지스터를 제작함으로써 접합영역의 효과 면적을 감소시키고 또한 특히 대용량 메모리 어레이에서 우려되는 누설전류 를 감소시킨다. 다른 D램 생산업체도 2백56M 및 1Gb D램 구조개발에 이와 유사한 접근방식을 적극적으로 채택하고 있다.

원가절감의 가장 큰 기회의 하나는 SOI를 사용하여 현존하는 디바이스 제작 라인에서 현존 회로선폭기술과 웨이퍼 크기로 고성능 고집적 칩을 과잉투자 없이 현자본만으로 생산할 수 있다는 데 있다. 전통적으로 CMOS기술은 그 성능의 향상을 회로선폭 축소화에 의존해 왔다. 그러나 이는 점점 더 값비싼 실습이 되며 시간이 경과함에 따라 더 큰 지름의 웨이퍼, 더욱 더 교묘하고 균일한 공정들, 그리고 새로운 툴들의 개발을 필요로 한다. 오늘날 새로운 state of the art"설비에 약 10억달러의 비용이 든다고 추정한다. 단지 기판 사용을 벌크 실리콘에서 SOI로 바꿈으로써 이러한 설비의 수명을 연장시킬수있다는 점은 대단히 매력적인 제안이 아닐 수 없다. 대다수 설비비용은 종전의 벌크 실리콘 제품의 라이프사이클 동안 벌써 상각되어 SOI프로덕트의작업비용만이 주된 원가요소가 된다.

따라서 CMOS기술에서 SOI로 이동함으로써 보다 다재다능한 SOI기판의 높은가격에도 불구하고 제품의 전체원가를 낮출 수 있다.

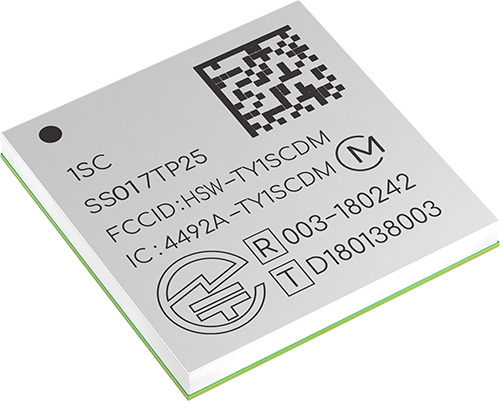

디지털 CMOS 응용분야에서의 두께범위를 고려할 때 두가지 SOI기술이 고려될 만하다. 그것은 SIMOX(separation by implantation of o.ygen)와 본딩이다.

본디드 웨이퍼방식은 실리콘층과 매립 산화층의 독립적인 선택을 가능하게한다. 본디드 SOI는 아날로그와 복합신호 디바이스 제품에 성공적으로 이용되고 있다. 본디드 웨이퍼가 이렇게 널리 수용되고 있는 것은 실리콘 디바이 스층과 매립 산화층 모두의 우수한 품질과 합리적 가격의 공급가능에 주된이유가 있다. 이중 본디드 웨이퍼의 매립 산화층은 열산화막 그 자체로서 다른 기술로는 그 품질의 추종이 불가하다. 일본 전자산업 개발협회(JEIDA)에 의한 조사를 포함한 많은 조사보고서는 웨이퍼 제조업체와 반도체산업체 모두 본디드 웨이퍼로 SOI를 제작하는 방식을 선호하고 있다고 지적한다.

현재 상용되고 있는 대다수 본디드 SOI는 그라인드와 폴리시(경면연마)기술 에 의하여 얇게 만드는 것으로서 본디드 디바이스 웨이퍼를 먼저 정밀연마하고 난 뒤에 경면연마로 목표두께까지 얇게 만드는 것이다. 이 기술은 BGSOI (backsidegrinding SOI)라고 부르며 2㎙에서 50㎙의 두께범위의 SOI층을 만드는 데 사용된다.

본디드 웨이퍼 방식의 가장 큰 결점은 CMOS의 얇은 Si두께 영역, 즉 1백~2백 나노미터까지 몇%의 균일성을 보장하면서 확장하는 것이 불가능하다는 인식 에 있어왔다. 그러나 지난 2년간 본디드 웨이퍼제작의 주요한 개발이 이루어져 이제는 얇고 균일한 본디드 SOI의 경쟁성 있는 가격에 공급이 현실적으로 가능하도록 되었다.

또 다른 성공적인 기술로 소위 BESOI(bond and etch back SOI)라는 것이 있다. 이 방식은 원래 래스키 등에 의하여 성공적으로 제안되었다. 이 방법에서는 먼저 도핑되지 않은 에피택셜필름을 매우 높게 도핑된 P 기판위에성장시킨다. 이 에피택셜 층은 산화된 핸들웨이퍼와 결합된다. 이어서 P층을 선택적으로 에치시켜 디바이스층(즉 undoped epita.ial층)에서 에칭이 멈추도록 한다. 이러한 원래 방식은 원리적으로는 가능했으나 낮은 에칭 선택도와 에칭되는 실리콘 양 때문에 조악한 품질의 두꺼운 SOI층만 만들 수있었다. 이후 여러가지 세부적인 기술들이 개발되었다. 그 예로 *보다 더 복잡한 에치스톱층들의 성장이 가능토록 진보된 에피택셜기술 *두께조절이 향상된 시작 실리콘 웨이퍼, 그리고 *우수한 그라인딩및 경면연마 기술을 이용하여 그라인딩과 에칭을 결부하는 방법 개발등을 들 수 있다. BGSOI의 경우에는상층 SOI 표면이 핸들 웨이퍼의 이면을 레퍼런스 플레인으로 삼는다. 따라서 최악의 경우 SOI의 전체두께편차(TTV)가 단일 웨이퍼의 TTV의 2배까지 될 수있다. 실제적으로 통상적인 BGSOI의 TTV가 이보다는 나은 편이긴 하나 전형 적인 상용 BGSOI로트의 경우 그 TTV가 약 1㎙정도로 높은 편이다. 이와 대조 적으로 BESOI는 에피택셜표면을 레퍼런스 플레인으로 사용한다. 이 경우 TTV 는 에치 스톱층의 균일성과 에칭선택도에 의하여 결정된다.

단면 투과전자현미경에 의한 광범위한 조사에서도 본디드 계면의 결함은 발견되지 않았다. 또한 SIMOX 재료에서 통상 발견되는 매립 산화층 내에 Si 개 재물도 발견되지 않았다. 다른 실험에서 매립 산화층의 인테그리티는 열 성장 산화막과 비슷한 수준으로 측정되었다. 한편 소수 캐리어 재결합 수명과 계면에서의 재결합 속도와 상관관계가 있는 마이크로웨이브 트랜전트 데케이 타임 측정에서 BESOI 웨이퍼는 다른 타입의 SOI에 비하여 높은 값인 25~50um 초의 데케이 타임을 보여 주었는데 이는 BESOI 재료내에 재결합 센터가 존재 하지 않는다는 것과 위 아래 계면 둘다 우수한 특성을 갖고 있다는 표시라고 볼 수 있다.

BESOI가 CMOS회로의 제작에 사용된 실례로 1백나노미터 두께의 BESOI 상에부분공핍화 설계를 바탕으로 하여 디바이스들을 LOCOS방법으로 격리하고 게이트 산화막을 4.2나노미터 두께로 만들었다. 극히 얕은 소스 드레인 연장영역을 형성하여 쇼트 채널 효과를 최소화하고 이중 폴리 게이트는 TiSz 스퍼 터링에 의하여 메털라이즈 시켰다. 그 결과 n 채널 트랜지스터는 우수한 문턱이하 특성과 "hard turn off"를 보여 주었다. SOI의 작동전력 공급을 감소 시키는 능력과 이미 매우 높은 성능을 보이고 있음은 현재 제작한 게이트 길이로서도 저전력 및 휴대형 디바이스 응용에 사용할 수 있음을 시사해 주고있다. SOI의 CMOS 응용이 타당하다는 점은 원가, 성능, 그리고 저전력 측면에서 볼때 확실하다. 생산규모의 비용효율이 뛰어난 기판의 준비는 반도체 제조업체 가 SOI를 기초로 하는 제품 계획을 실천하는 데 결정적으로 필요하다. 본디 드 웨이퍼 방식, 특히 BESOI는 비용 효율이 높고 고품질의 에피택셜 막의 SOI기판을 생산규모로 공급할 수 있는 잠재력을 제시하고 있다.

<번역:이동면MEMC사 공학박사>

많이 본 뉴스

-

1

테슬라, 중국산 '뉴 모델 Y' 2분기 韓 출시…1200만원 가격 인상

-

2

필옵틱스, 유리기판 '싱귤레이션' 장비 1호기 출하

-

3

'과기정통AI부' 설립, 부총리급 부처 격상 추진된다

-

4

'전고체 시동' 엠플러스, LG엔솔에 패키징 장비 공급

-

5

모바일 주민등록증 전국 발급 개시…디지털 신분증 시대 도약

-

6

은행 성과급 잔치 이유있네...작년 은행 순이익 22.4조 '역대 최대'

-

7

두산에너빌리티, 사우디서 또 잭팟... 3월에만 3조원 수주

-

8

구형 갤럭시도 삼성 '개인비서' 쓴다…내달부터 원UI 7 정식 배포

-

9

공공·민간 가리지 않고 사이버공격 기승…'디도스'·'크리덴셜 스터핑' 주의

-

10

MBK, '골칫거리' 홈플러스 4조 리스부채…법정관리로 탕감 노렸나

브랜드 뉴스룸

×

![]()