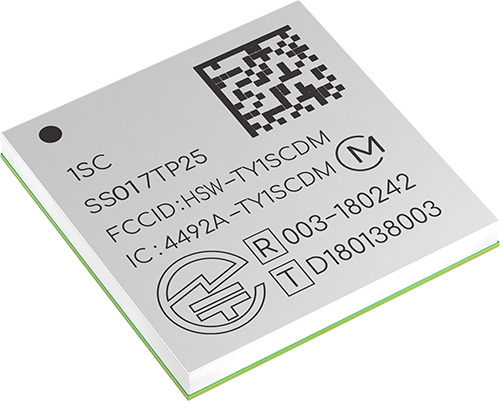

칩 선폭 3nm…기존의 30분의 1

나노기술의 급격한 발전으로 기존 칩의 30분의 1 크기의 소형 칩이 향후 3∼5년 내에 개발될 것으로 보인다.

이 소형 칩은 선폭이 일렬로 늘어선 원자 몇개 정도의 길이 밖에 안되는 실리콘 나노전선(nanowire)의 네트워크로 구성되며, 관련칩 제조를 위해 화학자들이 실험실에서 개발한 기술이 현재 반도체 공장에서 사용하는 전통적 사진석판 기술을 대신할 것으로 예상되고 있다.

현재 칩 제조시설이 만들 수 있는 칩 전선 선폭은 90㎚. 1㎚는 10억분의 1m인 반면 나노기술로 만든 나노전선 선폭은 3㎚에 불과하다. 이와 관련, 파사데나 소재 캘리포니아 공과대학 안드레 디혼 컴퓨터공학 조교수는 최근 스탠퍼드대학에서 열린 반도체 학술대회 ‘핫 칩스’(Hot Chips)에서 “현재 칩 기술이 원자 크기 규모에서 물질을 조종하는 수준에 이르렀다”며 이같이 예견했다. 그는 “나노 규모의 메모리와 시스템을 만드는 데 필요한 기술이 거의 다 개발된 상태”라고 덧붙였다. 디혼 교수는 찰스 리버, 패트릭 링컨, 존 새비지 등의 연구원들과 함께 나노전선을 공동 연구 중이다.

디혼 교수는 이날 논문 발표에서 획기적 기술을 발표하진 않았지만 대기업 연구원과 학계 연구원들이 최근 몇년 동안 공동으로 이룩한 각종 반도체 관련 기술의 개가들이 사진석판기술을 대체하는 데 종합적으로 사용될 수 있을 것으로 전망했다.

그는 연구결과 실리콘 나노전선이 금과 실란(silane)의 화학반응을 통해 길어질 수 있다는 점이 드러났다고 설명했다.

실란은 실리콘과 수소원자의 배합물질이다. 실리콘은 이같은 화학반응을 통해 해체되면서 6개 정도의 원자를 배열한 두께의 균일 결정체로 바뀐다. 바로 이 결정체가 실리콘 나노전선이다. 나노전선은 스스로 최소형 나노칩의 기본 구성단위가 되는 기다란 전선형태로 만들어 간다.

실리콘 칩 표면에 전선 무늬를 인쇄하기 위해 초점이 높은 렌즈를 사용하는 전통적 사진석판술(리소그래피)은 물리적 한계로 인해 15년 안에 사양화될 것으로 예상된다. 지금까지 칩 제조업체들은 18개월마다 칩 성능이 두배로 빨라진다는 이른바 ‘무어의 법칙’(Moore`s Law)을 맞춰 왔다.

사진석판술이 사양화되면 나노기술이 그 자리를 차지할 공산이 크다. 하지만 이날 회의 참가자들은 나노기술 상용화에 대해 단기간에는 어렵다는 반응이었다.

반도체 전문지 일렉트로닉디자인의 편집인 데이브 버스키는 지금까지의 리소그래피 기술 우회 노력이 인상적이긴 하지만 디혼 교수가 예측한대로 3∼5년 내에 이 기술이 대체될 것으로 보이지 않는다고 밝혔다. 그는 “연구원들은 보통 상용화 시기에 대해 낙관하는 경향이 있다”고 말했다. 다른 전문가들도 원자수준에서 화학반응을 통제할 수 있을지와 나노전선을 적절하게 시험할 수 있을지에 대해 의문을 제기했다.

디혼 교수는 그러나 그러한 문제들이 해결 가능하다고 강변했다. 그는 나노전선이 ㎓ 범위에서 작동할 가능성이 높지만 속도가 빨라질수록 전기저항이 문제를 일으킬 수 있다는 점을 지적했다.

<제이안기자 jayahn@ibiztoday.com>