SK하이닉스가 7세대 고대역폭메모리(HBM4E)부터 '하이브리드 본딩'을 적용한다. 하이브리드 본딩은 D램 위·아래를 구리로 직접 연결하는 기술이다. 현 HBM에 사용 중인 마이크로 범프(솔더 볼)와 접합 소재가 필요하지 않아 반도체 업계 큰 변화를 몰고 올 전망이다.

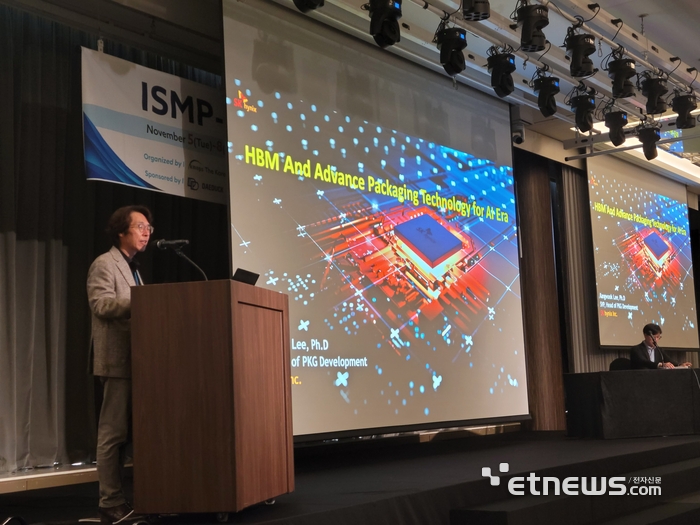

이강욱 SK하이닉스 부사장은 5일부터 8일까지 부산에서 열리는 한국마이크로전자및패키징학회 국제학술대회 'ISMP-IRSP 2024'에서 HBM 패키징 로드맵을 공개했다. 로드맵에 따르면 SK하이닉스는 HBM4E부터 D램 적층·접합에 하이브리드 본딩 기술을 활용하는 것으로 확인됐다. HBM4E는 SK하이닉스가 개발 중인 제품으로 2026년 양산 예정이다. 회사의 하이브리드 본딩 적용 시점이 구체화된 건 이번이 처음이다.

이 부사장은 “HBM 패키지 높이가 증가하면서 D램 적층 간격을 줄일 필요가 있다”며 “열 관리를 위해서도 하이브리드 본딩 방식 전환이 필요하다”고 말했다.

HBM4부터는 패키지 높이가 기존 720마이크로미터(㎛)에서 775㎛로 늘어난다. HBM4까지는 기존 적층 방식으로 이어갈 수 있지만, HBM4E부터는 새로운 패키징 공정 전환이 필요해졌다. 쌓아올리는 D램 간격을 최소화하고 열 관리 능력도 개선해야 하기 때문이다.

SK하이닉스는 현재 HBM 적층에 매스리플로우-몰디드언더필(MR-MUF) 방식을 쓰고 있다. D램을 마이크로 범프로 연결해 쌓은 후 빈 공간을 액상의 언더필 소재로 채워 굳히는 방식이다. 하이브리드 본딩은 마이크로 범프 대신 실리콘관통전극(TSV)에 있는 구리와 구리를 직접 연결한다. 언더필 소재도 필요없다. 위·아래 D램 간격을 최소화할 뿐만 아니라 마이크로 범프 저항도 없어 신호 전달이 빠르고 열 관리도 효율적이다.

이 부사장은 “하이브리드 본딩을 위해 화학적기계연마(CMP) 및 이물(파티클) 제어, 연결(인터커넥트) 수율 등 해결해야할 과제가 많다”면서도 “HBM3 12단으로 하이브리드 본딩 성능과 신뢰성을 파악한 결과 좋은 결과값을 얻었다”고 자신감을 드러냈다.

이 부사장은 20단 이상으로 추정되는 8세대 HBM 'HBM5'부터는 완전한 하이브리드 본딩 체제로 전환될 것으로 전망했다. 또 3차원(3D) 패키징 도입 가능성을 제기했다. 현재 HBM이 탑재되는 인공지능(AI) 가속기는 중앙에 프로세서(그래픽처리장치)를 두고 양 옆에 HBM을 배치한다. 2.5D 패키징이다. 3D 패키징은 프로세서 위에 HBM을 쌓는 방식으로, 실리콘 인터포저·기판 등 패키징 구성 요소의 대대적인 변화가 예상된다.

권동준 기자 djkwon@etnews.com