미세화 한계 극복…고성능 구현

파운드리 사업부 연구개발 추진

차세대 반도체 기술 주도권 확보

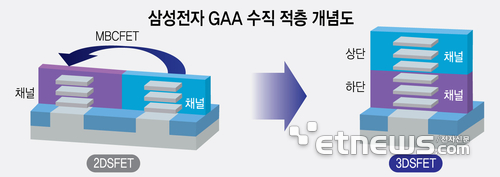

삼성전자가 시스템 반도체(로직) 트랜지스터를 수직으로 쌓는 '3D 적층' 기술을 개발한다. 3D 적층은 반도체 회로 미세화 한계를 극복하고 성능을 끌어올릴 방법으로 주목받는 기술이다. 업계와 학계에서 'CFET(상보형전계효과트랜지스터)'이라는 이름으로 연구를 이어오고 있다. 삼성전자가 기존 메모리에서만 적용됐던 3D 트랜지스터 구조 혁신을 시스템 반도체까지 확대, 첨단 반도체 기술 주도권을 확보할지 주목된다.

25일 업계에 따르면 삼성전자는 차세대 트랜지스터 구조인 'GAA(게이트올어라운드)'를 수직으로 쌓아올리는 R&D를 진행중인 것으로 파악됐다. 삼성전자 DS부문 반도체연구소와 파운드리 사업부에서 관련 R&D를 함께 추진하고 있다. 3D 구조를 차세대 GAA기술로 선택하고 본격적인 상용화를 위한 연구개발에 돌입한 것으로 풀이된다.

GAA는 트랜지스터 핵심 구성요소인 채널 4개면을 게이트가 둘러싼 형태로, 기존 3개면이 접합된 핀펫(FinFET) 대비 고성능·저전력 반도체를 쉽게 구현할 수 있다. 삼성전자는 지난해 3나노 공정을 GAA 구조로 세계 최초 양산한 바 있다. TSMC는 2나노부터 GAA 도입을 예고한 상태다.

삼성전자가 현재 연구 중인 3D GAA 구조는 '3DSFET'으로 불린다. 3차원, 3D 적층을 표현한 것으로 풀이된다. 현재 양산 중인 GAA는 하나의 트랜지스터를 옆으로 이어 붙이는 2차원(2D) 구조다.

반도체 공정이 미세화할 경우 전류 누설 등 셀 간 간섭으로 인한 문제와 반도체 면적 확보에 어려움을 겪게 된다. 이 한계를 극복한 방안이 GAA 트랜지스터를 수직으로 적층하는 것이다. 셀 간섭을 최소화하고, 보다 좁은 공간에 많은 트랜지스터를 집적할 수 있다. 마치 낸드 플래시 셀을 높은 단수로 쌓아 올려 성능을 끌어올리는 것과 같은 방식이다.

3D GAA는 지금까지 메모리에서만 통용되던 3D 적층 구조를 시스템 반도체까지 저변을 넓힌다는 데 의미가 있다. 3나노 이하 미세 공정에서 기존 핀펫 구조가 한계에 직면하자 GAA로 트랜지스터 구조로 패러다임이 바뀌듯 1나노 이하에서는 3D GAA 구조로의 전환이 이뤄진다는 것이 업계 중론이다.

선제적으로 GAA 양산에 성공한 삼성전자가 3D GAA까지 먼저 확보할 경우, 첨단 반도체 기술 경쟁 우위를 차지할 가능성이 높아진다.

업계 관계자는 “주요 반도체 기업이 시스템 반도체 트랜지스터를 수직으로 쌓는 3D 기술을 확보하기 위해 R&D에 적극 투자 중”이라며 “반도체 구조 혁신을 먼저 달성하는 기업이 시장 주도권을 쥐게 될 것”이라고 밝혔다.

권동준 기자 djkwon@etnews.com