고난도 트랜지스터 구현 성공

게이트·채널 접합면 넓혀 전력 효율 향상

5나노 핀펫보다 성능 23%↑·칩면적 16%↓

고객 요구 따라 와이어 시트 방식도 지원

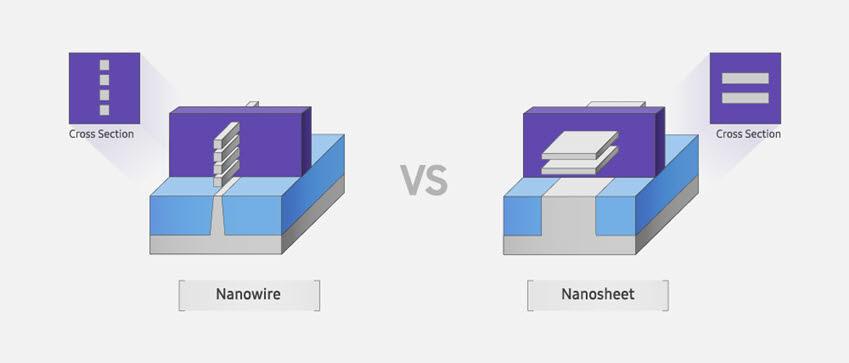

삼성전자 3나노 GAA 공정은 기술 난도가 높은 '나노시트' 형태로 트랜지스터를 구현했다. 초기 GAA 구조가 될 것으로 예상됐던 '나노 와이어' 방식을 바로 뛰어넘었다. GAA에 대한 삼성전자의 기술 자신감이 엿보인다. 삼성전자는 고객사 요구에 맞춰 나노 와이어와 나노시트 구조를 유연하게 적용할 방침이다.

현재 트랜지스터 구조 대세인 핀펫은 채널과 게이트 접합면이 3개다. 차세대 구조인 GAA는 두 가지 형태로 발전한다. 첫 번째는 얇은 원기둥 모양 채널이 게이트 안에 들어가 있는 나노 와이어 형태다. 게이트가 채널을 감싸는 고난도 기술이 적용된다. 그러나 채널과 게이트 접합면이 넓지 않아 전력 제어에 한계가 있다.

이를 개선한 것이 나노시트 구조다. 와이어 모양 채널을 보다 넓게 편 구조다. 게이트와 채널 간 접합면을 4개로 구현하면서 동시에 접합면 자체도 넓혔다. 게이트가 채널에 흐르는 전류를 제어하기 용이한 구조다. 삼성전자는 이 구조를 'MBCFET(Multi Bridge Channel FET)'이라고 명명했다.

주목할 부분은 삼성전자가 세계 최초로 3나노 GAA 양산에 나노 와이어가 아닌 나노시트 방식을 채택했다는 것이다. GAA 초기 구조로 예상됐던 나노 와이어를 뛰어넘어 한 단계 고도화된 GAA를 구현했다. 삼성전자 GAA 기술력이 이미 높은 수준에 올랐다는 방증이다.

이번에 양산하는 3나노 GAA는 5나노 핀펫 대비 전력은 45% 절감된다. 성능은 23% 향상되고 칩 면적은 16% 줄일 수 있다. 보다 다양한 기기 폼팩터에 적용할 수 있는 반도체 개발이 가능할 것으로 예상된다.

삼성전자가 나노시트 구조를 GAA 1세대(GAE)로 삼았다. 2세대(GAP)에서도 기술 성장 가능성을 남겨둔 것이다. 삼성전자는 “GAA 2세대 공정은 (5나노 핀펫 대비) 전력은 50% 절감, 성능 30% 성능 향상, 면적은 35% 축소된다”고 밝혔다.

다만 삼성전자가 나노 와이어 방식 GAA를 완전 배제한 것은 아니다. 고객사(팹리스)마다 원하는 GAA 구조가 다르기 때문이다. 요구하는 반도체 성능에 따라 나노 와이어와 나노시트 방식을 나눠 3나노 공정에 적용한다. 일종의 '투트랙' 전략이다.

◇GAE와 GAP=삼성전자가 게이트올어라운드(GAA) 세대를 구분하기 위해 독자적으로 사용하는 명칭. GAE는 'GAA 얼리(Early)'로 삼성전자 1세대 GAA 구조다. GAP는('GAA 플러스(Plus)'로 2세대다. 삼성전자는 내년 3나노 2세대인 GAA 플러스(3GAP)를 양산할 예정이다.

김지웅기자 jw0316@etnews.com