반도체 전자설계자동화(EDA) 툴 1위 업체 시높시스가 신규 제품을 내놓고 아날로그 칩 설계 시장을 공략한다. 이 분야는 케이던스가 대부분의 점유율을 갖고 있다.

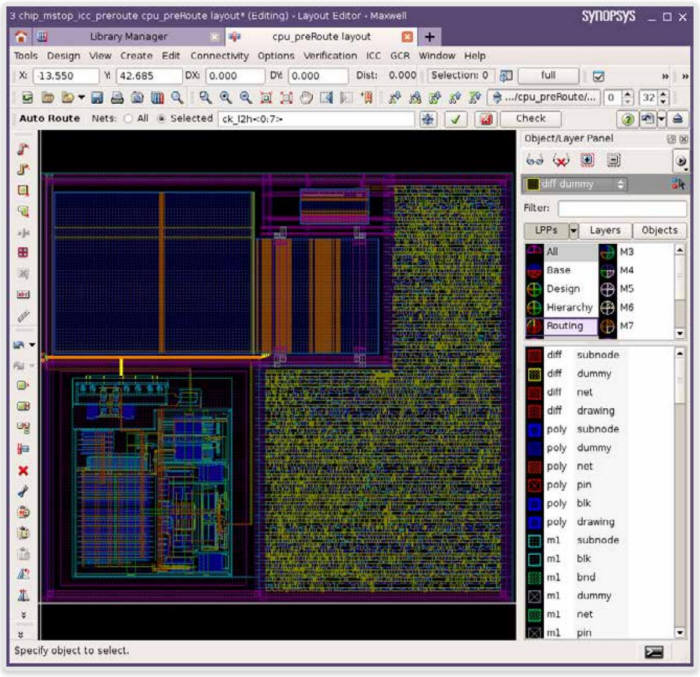

21일 시높시스는 신규 EDA 설계 툴 `커스텀 컴파일러`를 출시한다고 밝혔다. 핀펫(FinFET) 공정이 적용되는 첨단 IC를 포함해 아날로그, 디지털·아날로그 혼성신호 IC를 설계할 수 있는 툴이다. 칩 설계 과정을 눈으로 직접 보면서 작업을 할 수 있는 자동화 비주얼 어시스턴트 기술이 최대 강점이다. 디지털과 아날로그 블록을 동시에 불러와 설계 작업을 할 수도 있다. 과거에는 디지털과 아날로그 블록을 따로 그린 뒤 수작업으로 연결하는 식으로 작업을 했다. 많은 시간이 소요됐고 사람 실수로 칩 작동에 문제가 생기는 경우도 있었다.

데이브 리드 시높시스 제품 마케팅 이사는 “신제품을 활용하면 수일에 걸쳐 작업할 것을 단 몇 시간내 해결 가능하다”고 강조했다.

◇레이아웃·템플릿·코-디자인·인-디지인이 핵심

커스텀 컴파일러는 레이아웃, 템플릿, 코-디자인, 인-디자인 네 가지 툴이 핵심이다. 레이아웃 어시스턴트는 회로 배치, 배선 설계를 그래픽 환경에서 보다 쉽고 빠르게 수행한다. 설계자가 마우스로 배선을 방향만 지시하면 시스템이 자동으로 최적의 배선을 해 주는 식이다. 핀펫 등 최첨단 트랜지스터 구조를 그릴 때 정확한 `자동화`로 설계 시간을 크게 단축시켜준다는 것이 시높시스 설명이다.

템플릿 어시스턴트는 기존 그려놓은 레이아웃 패턴을 잘라내고 다른 곳으로 쉽게 붙일 수 있다. 잘 디자인된 레이아웃을 저장해뒀다가 필요할 경우 불러와서 사용하는 것도 가능하다.

코-디자인 어시스턴트는 디지털과 아날로그 회로 블록을 동시에 불러와 각 부분을 연결할 수 있다. 기존에는 수작업으로 했던 것이다. 코-디자인 어시스턴트에선 아날로그 회로를 만들어 배치시킬 수도 있다.

인-디자인 어시스턴트는 칩 설계를 하면서 검증을 실시하는 시스템이다. 커스텀 컴파일러에는 빠른 속도의 디자인룰체킹(DRC:Design Rule Checking) 도구가 내장돼 있다. 이를 통해 검증 시간을 크게 단축시킨다.

◇“케이던스 아날로그 툴 대체 가능”

시높시스는 케이던스가 장악하고 있는 아날로그 칩 설계 툴 시장의 대안으로 이번 신제품을 내세운다는 계획이다.

시높시스 커스텀 컴파일러의 코-디자인 어시스턴트는 케이던스의 아날로그 레이아웃 툴인 버추소(Virtuoso) 제품군의 기능이 구현된다. 일차 타깃은 시스템온칩(SoC), 디지털 아날로그 혼성신호 칩 설계, 생산 업계다. SoC 내에는 아날로그디지털 컨버터나 입출력(I/O) 등 몇 가지 아날로그 블록이 들어간다. 커스텀 컴파일러를 사용하면 디지털과 아날로그 블록을 동시 설계, 변경할 수 있고 이를 통해 시간 절약이 가능함을 강조할 계획이다. 혼성신호 칩 업체에도 동일한 강점을 내세운다.

시높시스에 따르면 일본 아사히카세이와 미국 GSI 테크놀로지가 설계 도구를 자사 커스텀 컴파일러로 교체했다. ST마이크로도 28나노 완전 공핍형 실리콘-온-인슐레이터(FD-SOI:Fully Depleted Silicon On Insulator) 프로세스에 맞춘 칩 설계 도구를 커스텀 컴파일러로 바꿨다. 대만 TSMC는 10나노 핀펫 공정에 이 제품을 활용할 계획이다. 7나노 공정의 경우 커스텀 컴파일러를 지원 제품으로 인증했다.

한주엽 반도체 전문기자 powerusr@etnews.com